Milan + 3D V-Cache = des EPYC Milan-X avec 768 Mo de L3 ! |

————— 10 Novembre 2021 à 08h59 —— 14028 vues

Milan + 3D V-Cache = des EPYC Milan-X avec 768 Mo de L3 ! |

————— 10 Novembre 2021 à 08h59 —— 14028 vues

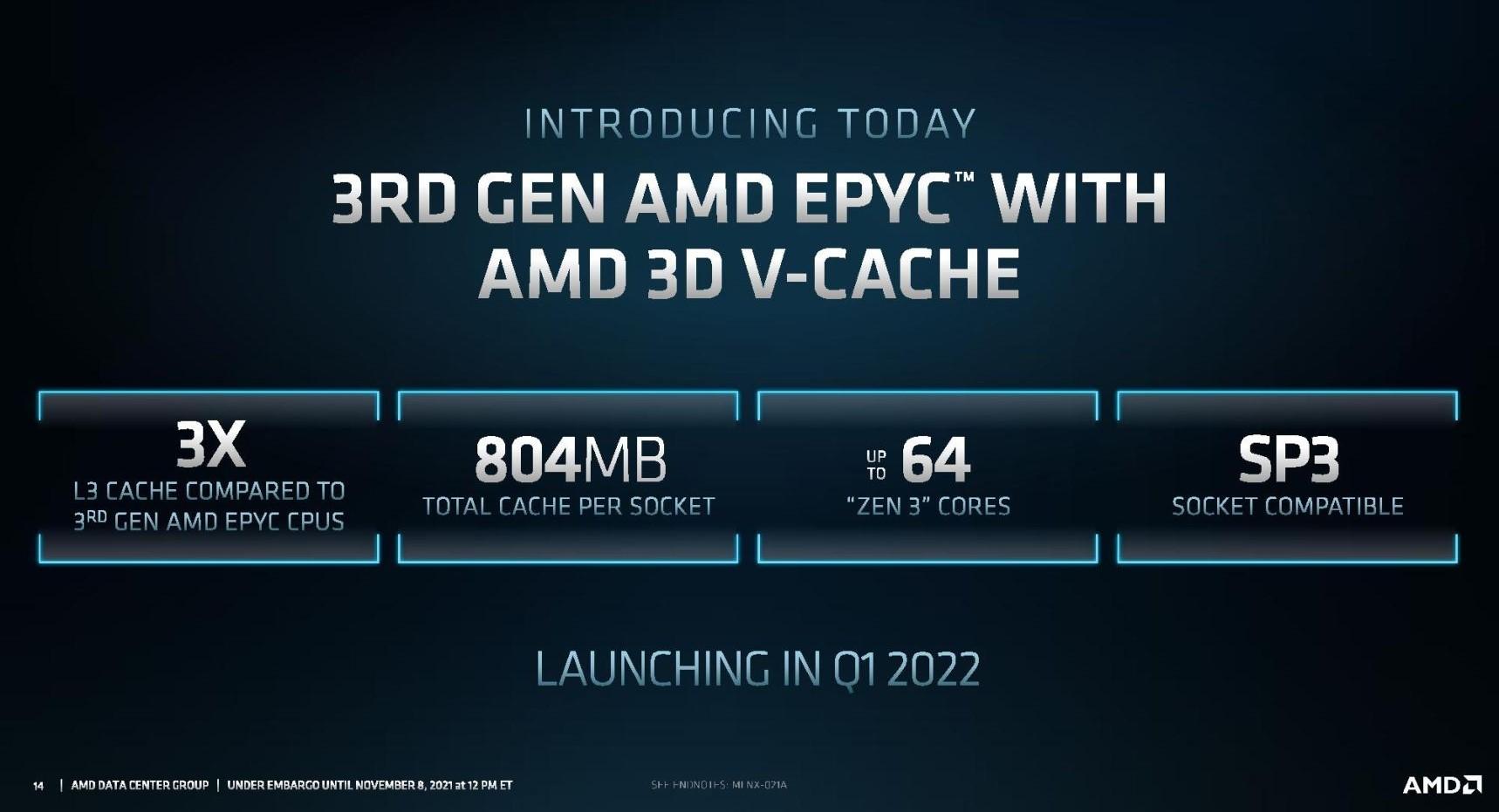

Comme prévu, en plus d'avoir confirmé sa roadmap pour l'après-Milan(— X) avec Genoa et maintenant aussi Bergamo, et annoncé la Radeon Instinct MI200, son premier GPU MCM, AMD a aussi dévoilé Milan-X ! Qu'est-ce ? Tout simplement de nouveaux modèles mis à jour pour la gamme EPYC d'AMD, mais dont les cores Zen 3 avec 32 Mo de cache L3 ont été complétés par un supplément de 64 Mo « simplement posés » par-dessus le cache existant, pour un nouveau total de 96 Mo par core, façon 3D selon la fameuse technologie de cache stacking dévoilée par AMD en juin dernier au Computex. Il s'agit bien évidemment du fameux 3D V-Cache ! Une prouesse rendue possible grâce à une variante optimisée du procédé N7 de TSCM, la couche additionnelle de cache L3 affiche très exactement une surface de 36 mm² (à titre indicatif, le die du core fait 80,7 mm²).

La gamme EPYC Milan-X sera composée de 4 références de 16 à 64 coeurs, toutes posséderont un cache L3 totalisant 768 Mo — ce qui veut dire qu'une machine double socket pourra proposer une quantité inégalée d'un peu plus de 1,5 Go de cache L3. Il est aussi intéressant de noter qu'AMD a confirmé que ses puces peuvent déjà supporter une quantité plus importante de piles L3, potentiellement au moins jusqu'à 4 si l'on en croit les paramètres de BIOS d'une machine EPYC Milan dénichés par HardwareLuxx, ce qui augure des évolutions bien intéressantes pour la suite. Milan-X sera parfaitement compatible avec le socket SP3 du matériel existant compatible avec Milan, mais AMD ne s'est malheureusement pas étalé sur les spécifications des nouveaux processeurs, il faudra attendre Q1 2022 pour connaître le contenu de la gamme, et les caractéristiques de fréquence et de puissance de chaque puce. Il n'est pas à écarter que le surplus de L3 impliquera une hausse de la consommation et peut-être une baisse légère de la fréquence maximale s'il s'agit de rester dans une enveloppe de 280 W.

Quant à ce que les grosses entreprises peuvent espérer de ces nouvelles bêtes, AMD ne s'est pas fait prier pour mettre en avant des gains de performances à deux chiffres pour différentes charges de travail, avec une moyenne de +50 % ! Par contre, le constructeur s'est bien gardé d'effectuer une comparaison directe avec les Xeon d'Intel et s'est contenté d'opposer Milan-X à Milan. AMD a aussi précisé qu'aucune modification logicielle ne sera nécessaire pour profiter des avantages du 3D V-Cache, mais l'entreprise a tout de même affirmé travailler avec ses partenaires pour élaborer des solutions optimisées. Milan-X s'adressera avant tout aux très grandes entreprises et AMD a déjà décroché des contrats avec Meta et Microsoft. Ce dernier a dans la foulée communiqué sur ses nouvelles machines virtuelles Azure HBv3 qui seront à base de Milan-X, avec des EPYC 7V73x 64 coeurs. De ce côté-là aussi ont été mises en avant des hausses à deux chiffres — parfois trois — des performances par rapport à une VM Azure à base de Milan ou de Skylake. Bref, tout s'annonce bien rose avec Milan-X, du moins tel que présenté. La lutte devrait être intéressante avec les futurs Sapphire Rapids d'Intel, qui proposeront une autre approche, avec l'option d'un cache HBM. En attendant, vu le supplément de wafer nécessaire et l'aspect inédit de ces nouveaux EPYC, il est fort probable qu'AMD les fera payer beaucoup plus chèrement que les EPYC Milan.

![Enlarge your pe...icture Oh, ça scale bien, hein ! [cliquer pour agrandir]](/images/stories/_cpu/7nm_amd/microsoft-scaling-perf-milan-x-epyc-azure-vm_t.png)

En tout cas, même en omettant le fait que les chiffres avancés l'autre jour tiennent avant tout du marketing, le 3D V-Cache n'en semble pas moins très prometteur. On ne peut donc qu'être d'autant plus impatient de voir la technologie débarquer dans le mainstream avec des Ryzen — qu'AMD ne se gênera sûrement pas de nommer « Ryzen 6000 » si les gains de performances sont d'un niveau semblable. Rappelons que ceux-ci seront dévoilés pendant le premier trimestre de l'année prochaine. (Source : AMD, Anandtech, Tom's)

| Un poil avant ?Noctua envoie son ventirad low profile sur LGA1700 | Un peu plus tard ...ACER rejoint le club des 32/144/3840, kezako ? |  |