Regardons plus en détail le 3D V-cache des prochains CPU AMD |

————— 08 Juin 2021 à 14h41 —— 30555 vues

Regardons plus en détail le 3D V-cache des prochains CPU AMD |

————— 08 Juin 2021 à 14h41 —— 30555 vues

La semaine dernière, nous vous présentions la dernière nouveauté technologique que veut pousser AMD dans leurs CPU d'ici quelques mois : le 3D V-cache, une technique qui permet l'empilement des caches de L3 afin d'apporter plusieurs avantages, comme une densité plus élevée ou des débits supérieurs. Toutefois, il convient d'apporter plus de détails sur cette innovation qui a déjà été vue par le passé sur plusieurs segments de l'électronique à basse consommation. Alors c'est parti, mettons les mains dans le cambouis et déchiffrons tout ça.

Rien à voir avec nos habituelles profanations sur les fuites, nous allons nous intéresser à la partie purement électronique avant de chercher les avantages et inconvénients de cette technologie. En effet, les technologies dites 2.5D et 3D sont devenues de plus en plus fréquentes sur le segment des puces à faible consommation, car des dies de petite taille sont plus simples à mettre en œuvre - et moins couteux - que des monstres dédiés au HPL - le High Power Logic, terme regroupant les unités de traitement (ASIC, CPU, FPGA...) de forte puissance. Au-delà des annonces flamboyantes de Lisa Su, il convient de prendre en compte que de base nous avons le droit à une technologie 3D, mais qui reste exploitée en 2.5D.

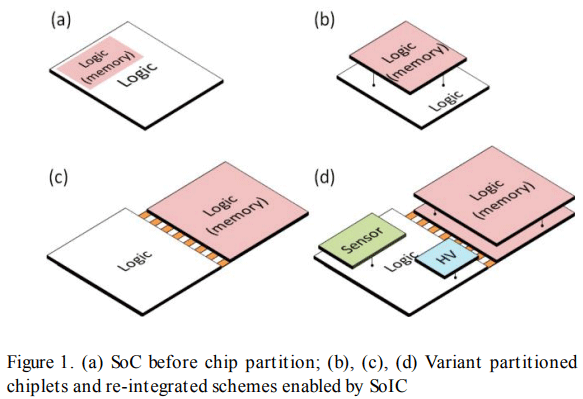

Exemples de topologies 2D (a), 2.5 D (b et c) et 3D (d).

Pour mieux comprendre le principe de base, AMD s'appuie très probablement vu les chiffres annoncés sur le SoIC mis au point par TSMC, une technologie qui permet la création de circuits 3D purs grâce à l'utilisation de contacts directs ou de TSV, des fils de cuivres qui traversent le die, comme sur les technologies d'Intel. Par contre, pour des raisons de cout de R&D et probablement de vitesse, cette technologie va être appliquée dans un premier temps sur des puces Zen3, qui ne sont pas adaptées dès le départ à ce type d'utilisation, réalisant des empilements de 2 puces maximum, face contre face - face-to-face - et de circuits similaires. De ce fait, nous parlons donc de technologies 2.5D pour l'instant, car il est impossible sur cette première génération d'empiler des puces différentes à l'infini.

Par contre, il est très probable à l'avenir de voir des empilements de couches de 3D V-cache sans problème en passant au face contre dos - F2B ou face-to-back - dès les générations Zen4, avec cette fois-ci un empilement directement sur les CCD du CPU. Une grosse innovation qui sera rendue possible grâce aux travaux de TSMC à ce sujet depuis quelques années déjà, et un tel développement était pressenti depuis quelques mois. En revanche, il convient d'étudier maintenant pourquoi passer à cette étape supérieure.

Empiler les modules de mémoire, c'est une chose que l'on voit depuis l'apparition des puces HBM, et dans le computing depuis les puces basées sur le Foveros d'Intel - Lakefield, mais aussi quelques FPGA. Ici, nous avons la première annonce - il n'est pas impossible d'avoir des surprises ailleurs - de l'utilisation de ces technologies 3D dans la création de puces HPL grand public, et cela va très probablement changer les choses pour nos futurs CPU et GPU.

![Ultra bouzotron HD max def mise en œuvre du SoIC pour les premier CPU 3D de chez AMD [cliquer pour agrandir]](/images/stories/_cpu/gravure_nm/wikichip-amd-vcache-cartoon_t.png)

Bien que dans un premier temps cela reste limité à du 2.5D, AMD utlise des méthodes de conception proches des circuits 3D.

Premièrement, le passage en 3D permet d'optimiser le câblage interne et de réduire la longueur des pistes pour une même surface, ce qui a des incidences intéressantes sur les performances. Car en améliorant le routage, les temps de propagation - le temps pour aller d'un point A à B d'un signal électrique - deviennent plus faibles, réduisant la latence et autorisant des montées à des fréquences plus élevées. Et pas de blagues, malgré les distances en apparence courtes, cela joue réellement de nos jours, le passage en 3D permet donc de gagner en latence et en débit, surtout sur des dies de "grande taille" comme employé sur un CPU.

Autre avantage, c'est que cette optimisation du câblage réduit aussi les pertes énergétiques lors des communications via l'interconnect, un sujet important lorsqu'un SoC - comme un CPU Ryzen - est divisé en chiplets. Par exemple, sur Lakefield, il est estimé que les communications coutent 0,15 pj/bit, où le 3D V-cache - s'il est réellement basé sur les technologies connues de chez TSMC - pourrait couter que 0,05 pj/bit, soit 3 fois moins. Les derniers chiffres connus pour les interconnects des puces Zen donnent au mieux une efficacité de 2 pj/bit, soit 50 fois plus que ce que semble offrir le 3D V-cache, ce qui amènerait à obtenir des CCD moins gourmands et moins chauds.

Enfin, fabriquer en 3D permettra d'améliorer grandement les process de fabrication et la miniaturisation. En effet, la densité plus élevée des connexions entre dies donnera plus de transistors possibles, et facilitera la démocratisation des unités spécialisées. Car avec une topologie en F2B, il sera possible d'empiler des chiplets différents et avec des intérêts particuliers, sans devoir agrandir les dies. Alors non, pour l'instant vous ne verrez pas des couches de CCD, puisqu'il sera difficile de les faire refroidir, par contre ajouter des unités de gestions de l'alimentation, des capteurs, des unités dédiées à l'IA ou au chiffrement, les puces d'I/O...

![Ultra bouzotron HD max def méthode de conception 3D via F2B [cliquer pour agrandir]](/images/stories/_cpu/gravure_nm/wikichip-hybrid-bonding-flow-repeat_t.png)

Le SoIC permettrait d'améliorer la densité des puces en empilant différents éléments au-dessus des unités de traitement.

Passer en 3D permettra donc de supprimer certains soucis rencontrés par les concepteurs de puces lorsqu'il faut passer en chiplet ou en multi die. Ici, nous ne sommes pas encore sur une immense innovation de la part d'AMD, mais plutôt d'une preuve de concept, une tentative pour valider l'intérêt d'une telle technologie de nos jours. Cela va se regrouper avec d'autres rumeurs et fuites en tout genre, comme l'utilisation de chiplets sur les GPU, et il est très fort probable que les rouges ne seront pas les seuls à ce sujet, par contre, ils pourraient être les premiers à communiquer et commercialiser des puces HPL en 2.5D pour le grand public. Un passage à une étape supérieure, qui s'éloignera un peu de la course à la miniaturisation et en lancera probablement une nouvelle : la course à l'empilement, qui elle a déjà commencé chez les fabricants de NAND. (source : Wikichip)

| Un poil avant ?PNY donne les raisons de la grosse baisse de l'endurance de son SSD XLR8 CS3030 | Un peu plus tard ...Test • GIGABYTE RTX 3080 Ti EAGLE |  |