Intel rentre dans la course des die en 3D complexes, les processeurs de demain ? |

————— 19 Mai 2020 à 16h52 —— 12585 vues

Intel rentre dans la course des die en 3D complexes, les processeurs de demain ? |

————— 19 Mai 2020 à 16h52 —— 12585 vues

Si l'annonce de Comet Lake ressemble plus à un signe que pour l'instant Intel rencontre des difficultés à innover pour le grand public, dans ses recherches sur l'amélioration de la construction des dies le géant bleu n'est pas en reste pour autant. Les premières améliorations afin d'explorer la voie des chiplets et design en 2.5D a déjà été ouverte il y a 2 ans avec les processeurs Kaby Lake G, ouvrant la porte à de nouvelles possibilités qui ne sont toujours pas tant que ça exploitées depuis malheureusement. Cependant, celle-ci n'est pas jetée aux oubliettes, car elle est encore utilisée pour la production des FPGA, qui ont besoin d'un interconnect plus rapide.

Rien de tel qu'un petit rappel datant de 2018 made in Intel pour se remémorer les débuts du 2.5D bleu.

Une autre technologie du fondeur qui ressemble plus à de la 3D utilisée est Foveros, un système qui amène à des communications verticales à travers les dies pour les empiler et en faire des puces pouvant exploiter plus facilement les stacks de HBM par exemple. La fusion de ces deux technologies a donné le Co-EMIB, mais au final le coût de cette méthode est jugé trop important pour donner des développements intéressants. Et c'est là que le nouveau challenger d'Intel entre en jeu, et cette fois en pure 3D : le ODI, pour Omni Directionnal Interposer.

![Enlarge your pe...icture petit résumé visuel du système ODI [cliquer pour agrandir]](/images/stories/_cpu/intel-sm-brief-odi-wikichip_t.jpg)

Présentation simplifiée de l'implémentation concrète du ODI.

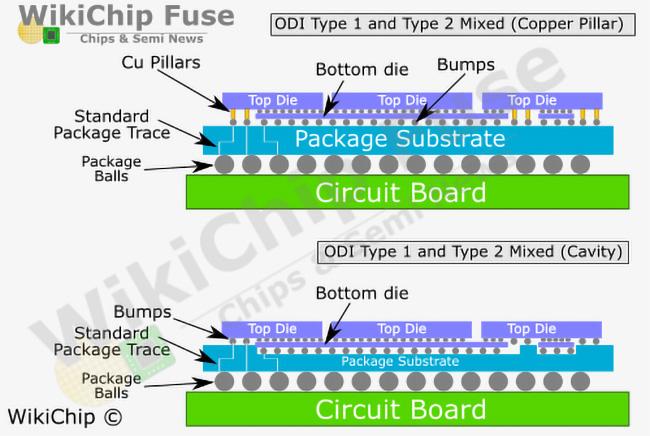

Teasé par les bleus l'été dernier, le système permet d'empiler directement les différents dies les uns sur les autres sans passer par un interconnect quelconque, avec deux types : le OD1, qui se base sur un empilement partiel afin de garder des surfaces de dissipation de chaleurs - dans le cas de la création d'un pont entre deux puces puissantes - et le OD2, qui met des puces plus petites entièrement sous la puce principale, ce qui peut être utile dans le cas de connexions plus directes, comme les contrôleurs mémoire ou les gestions des I/O. Les deux méthodes peuvent être utilisées en même temps afin d'améliorer l'efficacité globale et de créer des montages totalement en 3D.

Mais depuis une amélioration est subvenu : les puces situées en dessous peuvent être "enterrées" dans des cavités faites directement dans le substrat qui sert de support, afin de réduire l'utilisation de piliers de cuivre pour les échanges verticaux. L'avantage de cette solution est de faciliter la construction des puces, ce qui permettrait de rendre plus accessible la solution.

Présentation schématisée des deux méthodes : en surface avec pilliers de cuivre ou en enterrant les dies.

Mais finalement, pourquoi parler de tout ça maintenant nous direz-vous ? Et bien tout simplement que Intel va devoir sortir de nouvelles armes autres que ses process de gravure qui eux ont plus de mal à se développer, et qu'il a déjà été démontré que l'intégration des chiplets sera nécessaire pour exploiter au mieux les gravures les plus fines. Et que depuis 2018, les méthodes 2.5D et 3D ont eu le temps d'évoluer, avec un Co-EMIB mature aujourd'hui. Ce qui permettrait d'espérer que les bleus pourraient enfin sortir de leur boucle infernale du refresh à outrance à partir de cette fin d'année, et que les prochaines architectures pourraient être le début d'une nouvelle ère. (source : Wikichip)