RDNA 3 et les Dual-Issue CU : toujours plus de spéculations |

————— 09 Novembre 2022 à 19h29 —— 21280 vues

RDNA 3 et les Dual-Issue CU : toujours plus de spéculations |

————— 09 Novembre 2022 à 19h29 —— 21280 vues

Il y a quelques jours à peine, un sympathique cliché officiel permettait d’observer de près le die des RX 7900 XT(X), l’occasion rêvée pour tenter de découvrir quelle disposition logique se cachait sous le capot. Fort de discussions animées avec des experts du domaine, notre cher confrère @Locuza_ a complété et revu ses annotations, de quoi passer la soirée au jeu des 4 différences !

A couple of improvements and fixes follow this thread.@cha0shacker already pinged me a few days ago, showing that the high-level module still looks very RDNA1/2 like, meaning WGPs are still being used, as also stated in LLVM/Linux comments.

— Locuza (@Locuza_) November 7, 2022

1/x https://t.co/PknQ35BEXr pic.twitter.com/0jRAU5gkco

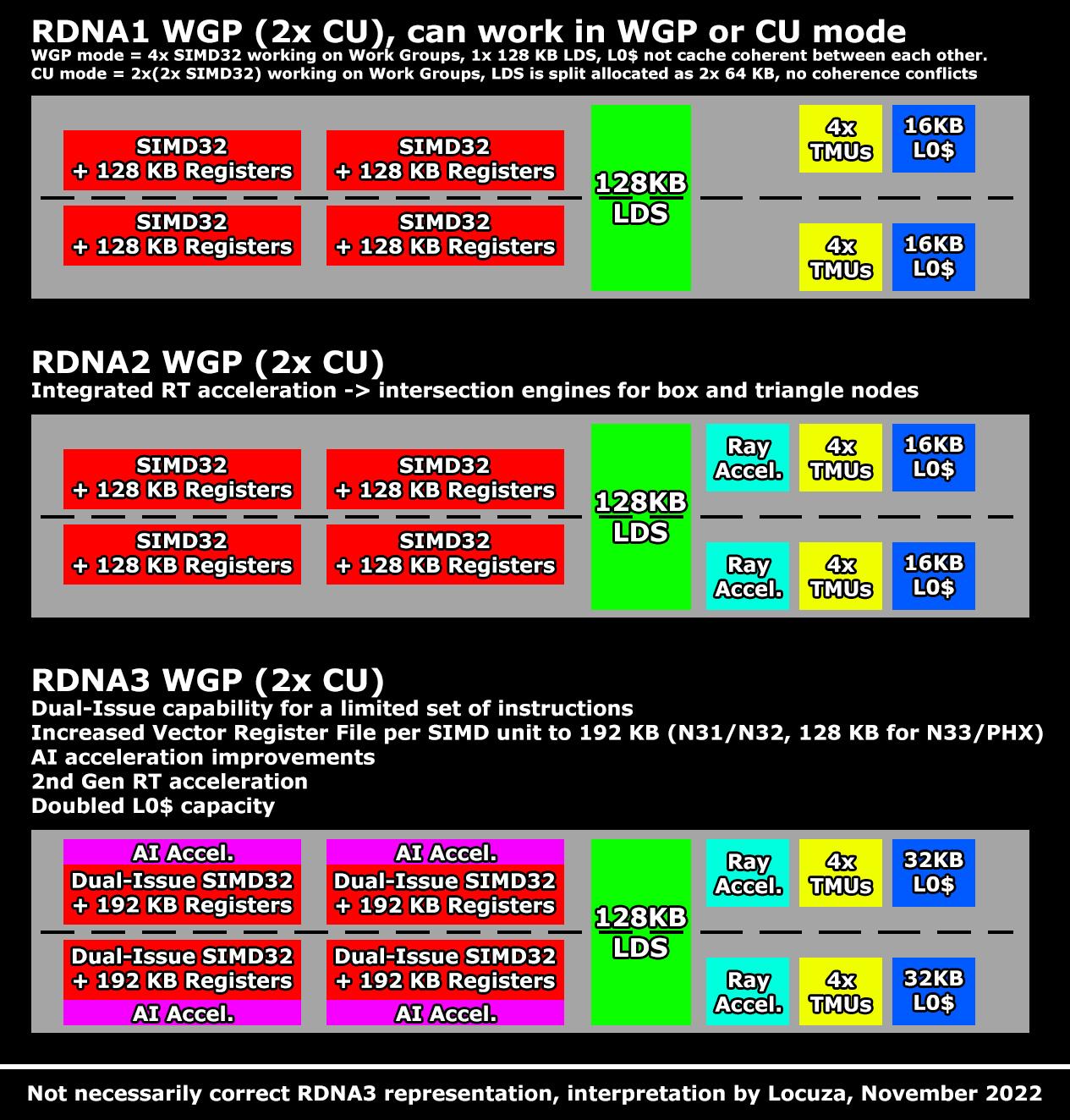

Si nous n’allons pas pinailler sur la majorité de ces détails, l’un d’entre eux revêt une importance cruciale : l’organisation logique des nouveaux CU. En effet, avec RDNA 3, AMD a annoncé avoir gonflé ces derniers de manière à accepter deux instructions par cycle et ainsi doubler leur puissance de calcul, ce que certains ont interprété comme un doublement effectif de leur quantité ; tandis que nous supputions une fusion CU-WGP. Raté !

En effet, les WGP sont toujours présents et combinent toujours bien 2 CU dual-issue soit 4 SIMD32 dual-issue, au passage chacune gonflée d’un accélérateur d’IA. Cependant, le doublement du débit FP32 de ces CU n’est, en fait, pas valable pour toutes les opérations : si les FMA (fused multiply-add) ont bien droit à deux unités au sein des nouveaux CU, tel n’est pas le cas des instructions faisant usage de l’accélérateur d’IA (dont toutes celles faisant partie de l’extension DP4a), des Rapid Packed Math (opérations vectorielles en FP16 à quadruple vitesse) ni les opérations de calcul entier 15/24/32 bits. Dans la pratique, un dual-issue CU ressemble dans l’esprit à un module de feue l’architecture Bulldozer : deux files d’instructions, mais certaines unités communes, d’autres non. À l’exception que Bulldozer partageait les unités de calcul flottant, et que la réservation de l’unité était effectuée dynamiquement selon l’ordre d’ordonnancement des processus, là où RDNA 3 se doit d’intégrer ces restrictions dès la compilation des kernels GPU. À voir dans les semaines qui suivent ce qu’il en sera en pratique !

| Un poil avant ?La famille RTX 4080 GIGABYTE en photo ! | Un peu plus tard ...Chieftec introduit un boitier qu'est sobre et pas trop grand |  |