Advancing AI 2025 : AMD dévoile ses plans pour l’IA et les serveurs jusqu’en 2027 |

————— 13 Juin 2025 à 14h52 —— 23031 vues

Advancing AI 2025 : AMD dévoile ses plans pour l’IA et les serveurs jusqu’en 2027 |

————— 13 Juin 2025 à 14h52 —— 23031 vues

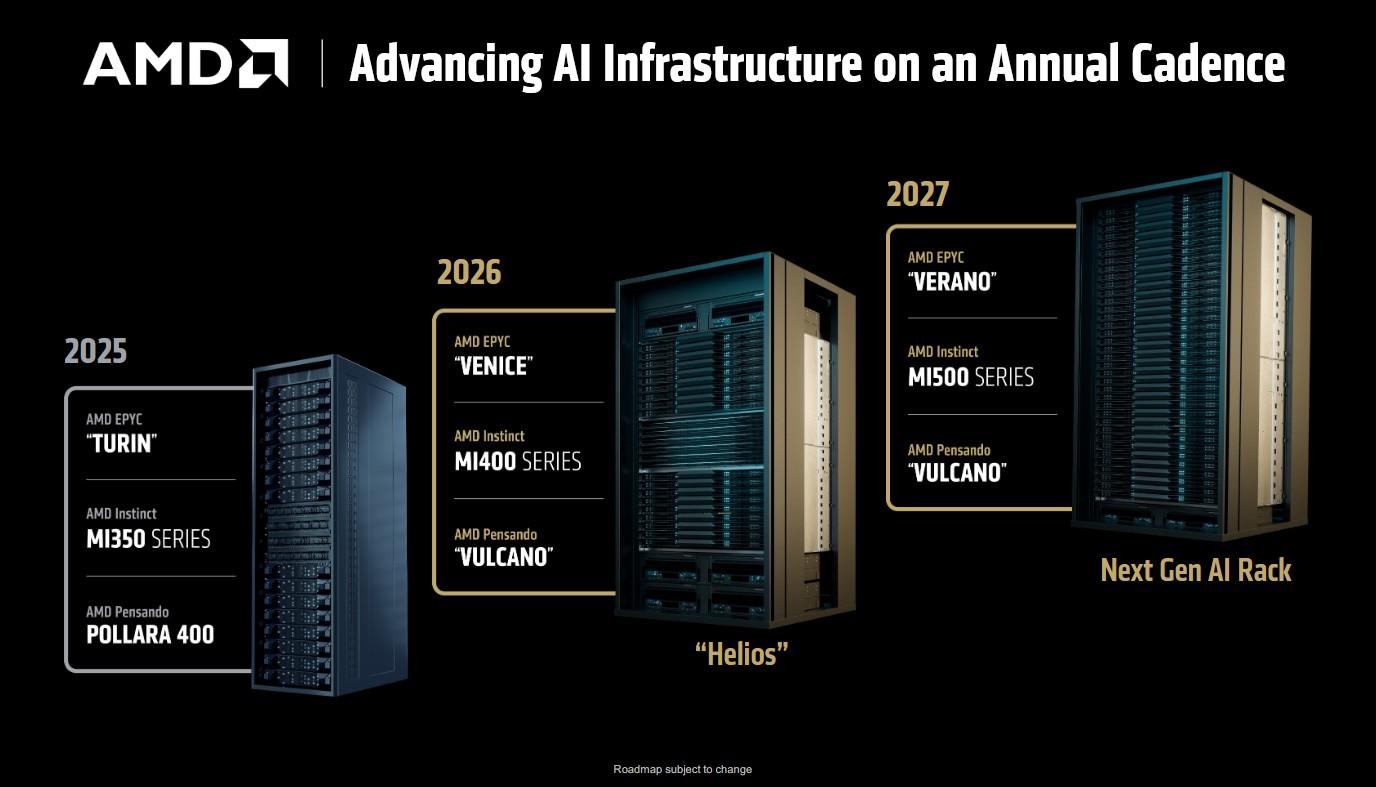

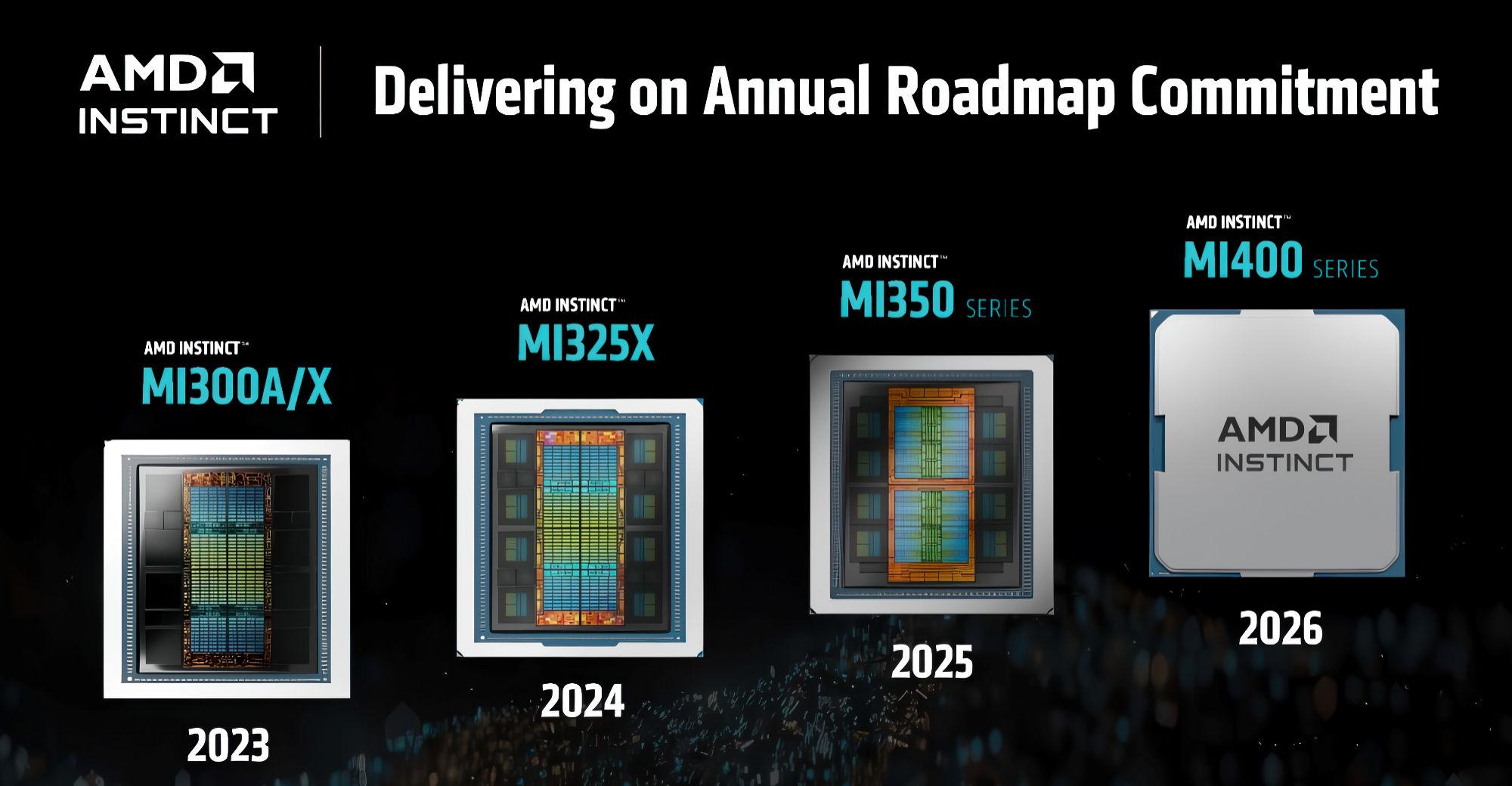

À l’occasion de son évènement Advancing AI 2025, AMD a levé le voile sur ses projets pour les secteurs de l’intelligence artificielle et du calcul haute performance. Parmi les annonces phares, on retrouve les accélérateurs Instinct MI350X et MI355X, déjà évoqués plus tôt dans la semaine, ainsi qu’une feuille de route étendue côté processeurs EPYC, avec l’introduction des générations Venice (2026) et Verano (2027).

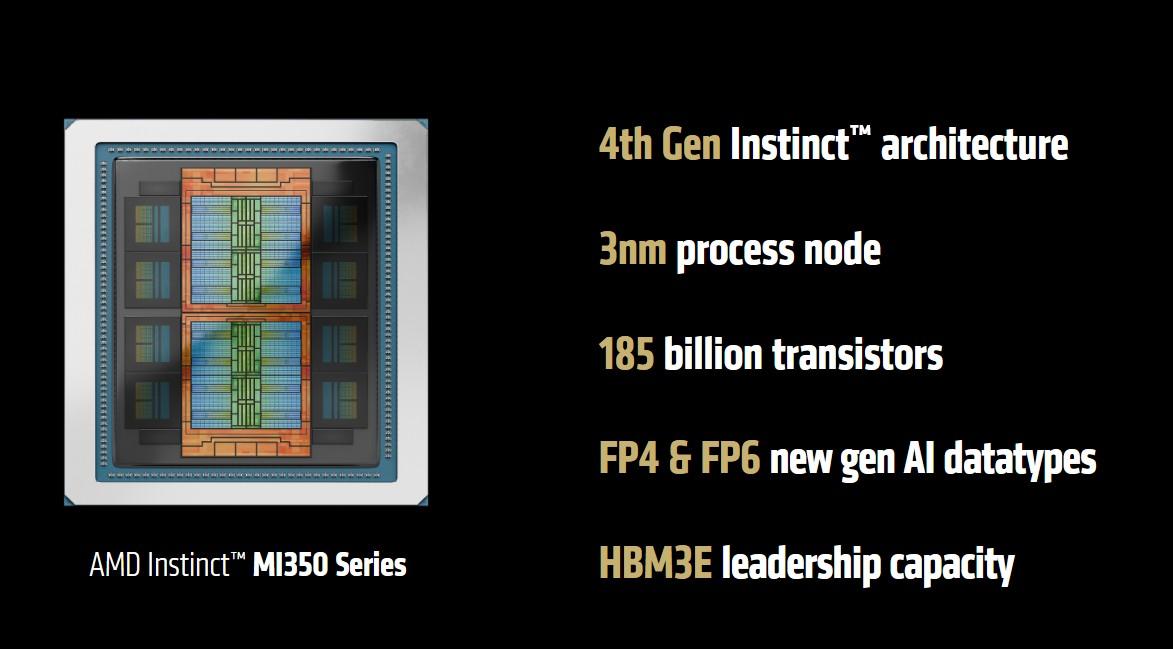

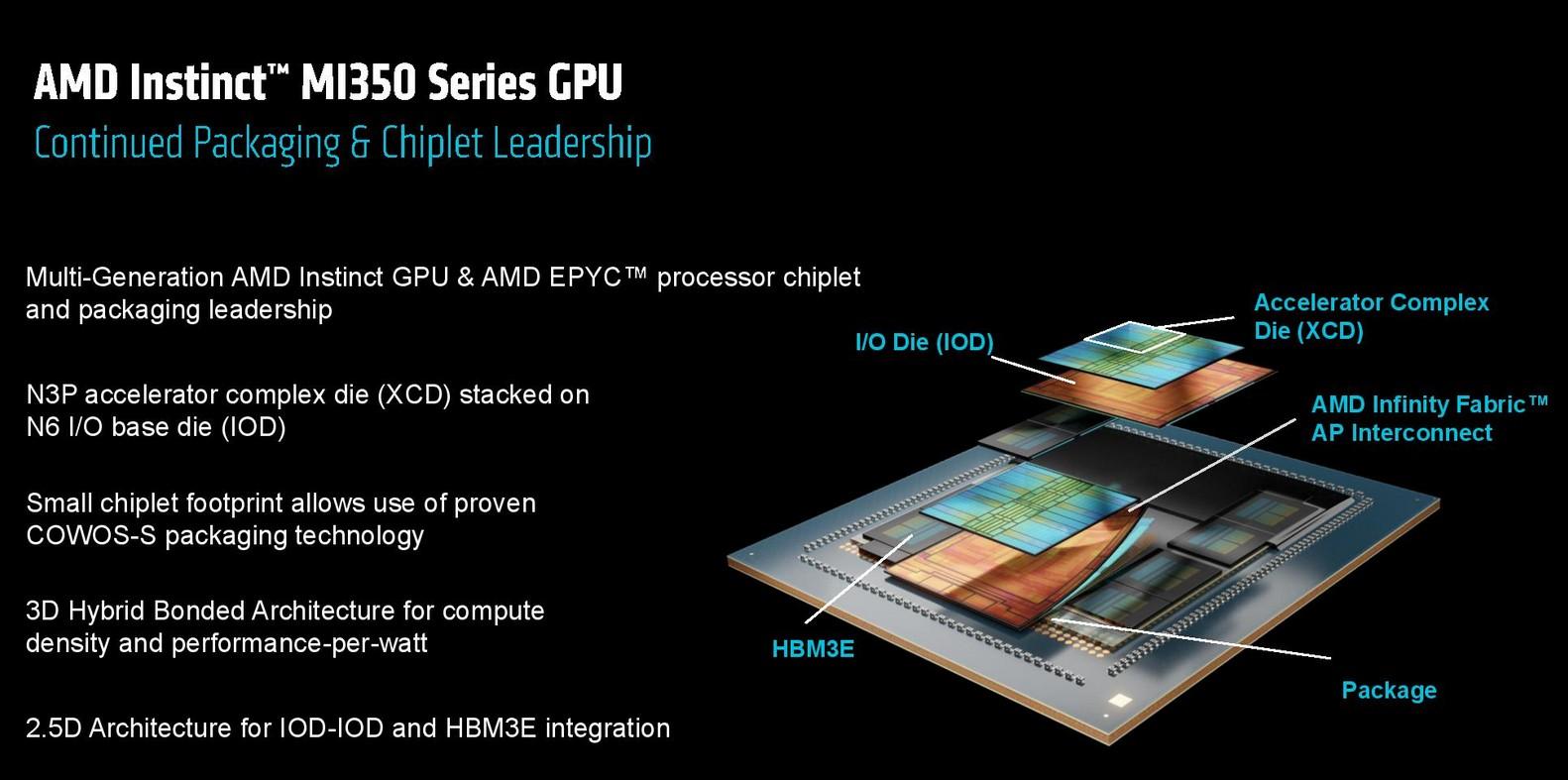

La série MI300 s’élargit avec l’arrivée des MI350X et MI355X, tous deux reposant sur la nouvelle architecture CDNA 4. Celle-ci introduit la prise en charge des formats FP4 et FP6 pour l’inférence IA. Les deux accélérateurs partagent un même silicium gravé en N3P (3 nm) chez TSMC pour les chiplets XCD ; le chiplet IOD est élaboré en N6.

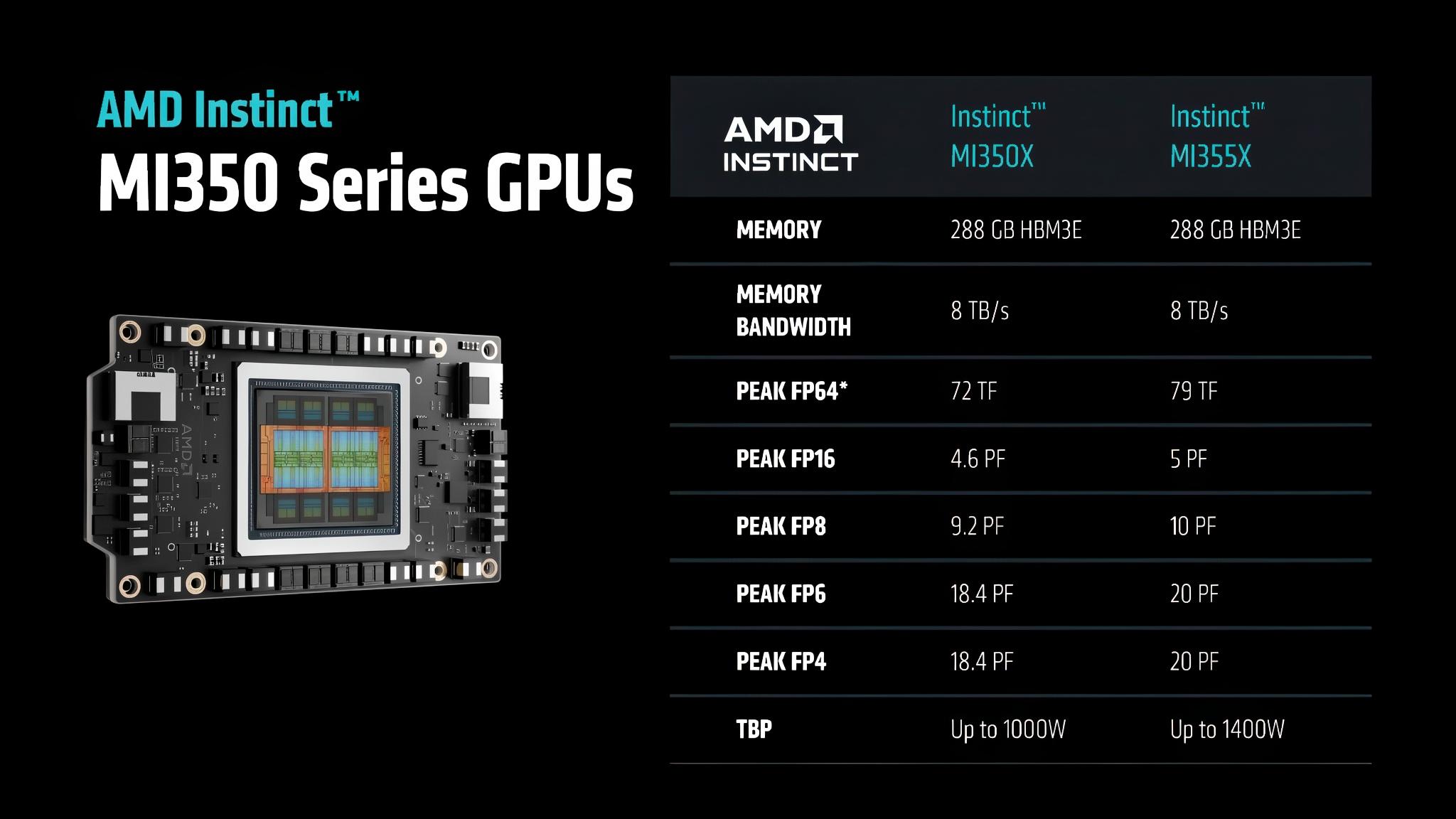

Ils embarquent chacun 256 unités de calcul, soit 16 384 processeurs de flux, et 288 Go de mémoire HBM3e avec une bande passante de 8 To/s. Le MI355X se distingue par une enveloppe thermique plus élevée, pour des performances logiquement supérieures à celles du MI350X. La commercialisation est prévue pour le troisième trimestre 2025.

| Type | AMD Instinct MI325X GPU | AMD INSTINCT MI350X GPU | AMD INSTINCT MI350X PLATFORMe | AMD INSTINCT MI355X GPU | AMD INSTINCT MI355X PLATFORMe |

|---|---|---|---|---|---|

| GPUs | Instinct MI325X OAM | Instinct MI350X OAM | 8 x Instinct MI350X OAM | Instinct MI355X OAM | 8 x Instinct MI355X OAM |

| Architecture | CDNA 3 | CDNA 4 | CDNA 4 | CDNA 4 | CDNA 4 |

| Mémoire | 256 Go HBM3E | 288 Go HBM3E | 2,3 To HBM3E | 288 Go HBM3E | 2,3 To HBM3E |

| Bande passante mémoire | 6 To/s | 8 TB/s | 8 To/s par OAM | 8 To/s | 8 To/s par OAM |

| FP64 Performance | - | 72 TFLOPs | 577 TFLOPs | 78,6 TFLOPS | 628,8 TFLOPs |

| FP16 Performance | 2,61 PFLOPS | 4,6 PFLOPS | 36,8 PFLOPS | 5 PFLOPS | 40,2 PFLOPS |

| FP8 Performance | 5,22 PFLOPS | 9,2 PFLOPs | 73,82 PFLOPs | 10,1 PFLOPs | 80,5 PFLOPs |

| FP6 Performance | - | 18,45 PFLOPS | 147,6 PFLOPS | 20,1 PFLOPS | 161 PFLOPS |

| FP4 Performance | - | 18,45 PFLOPS | 147,6 PFLOPS | 20,1 PFLOPS | 161 PFLOPS |

| Typical Board Power (TBP) | 1000 W Peak | 1000 W Peak par OAM | 1000 W Peak par OAM | 1400 W Peak par OAM | 1400 W Peak par OAM |

![Ultra bouzotron HD max def MI300X vs MI355X AMD [cliquer pour agrandir]](/images/stories/_ia/indices-perfo-mi350-amd_t.jpg)

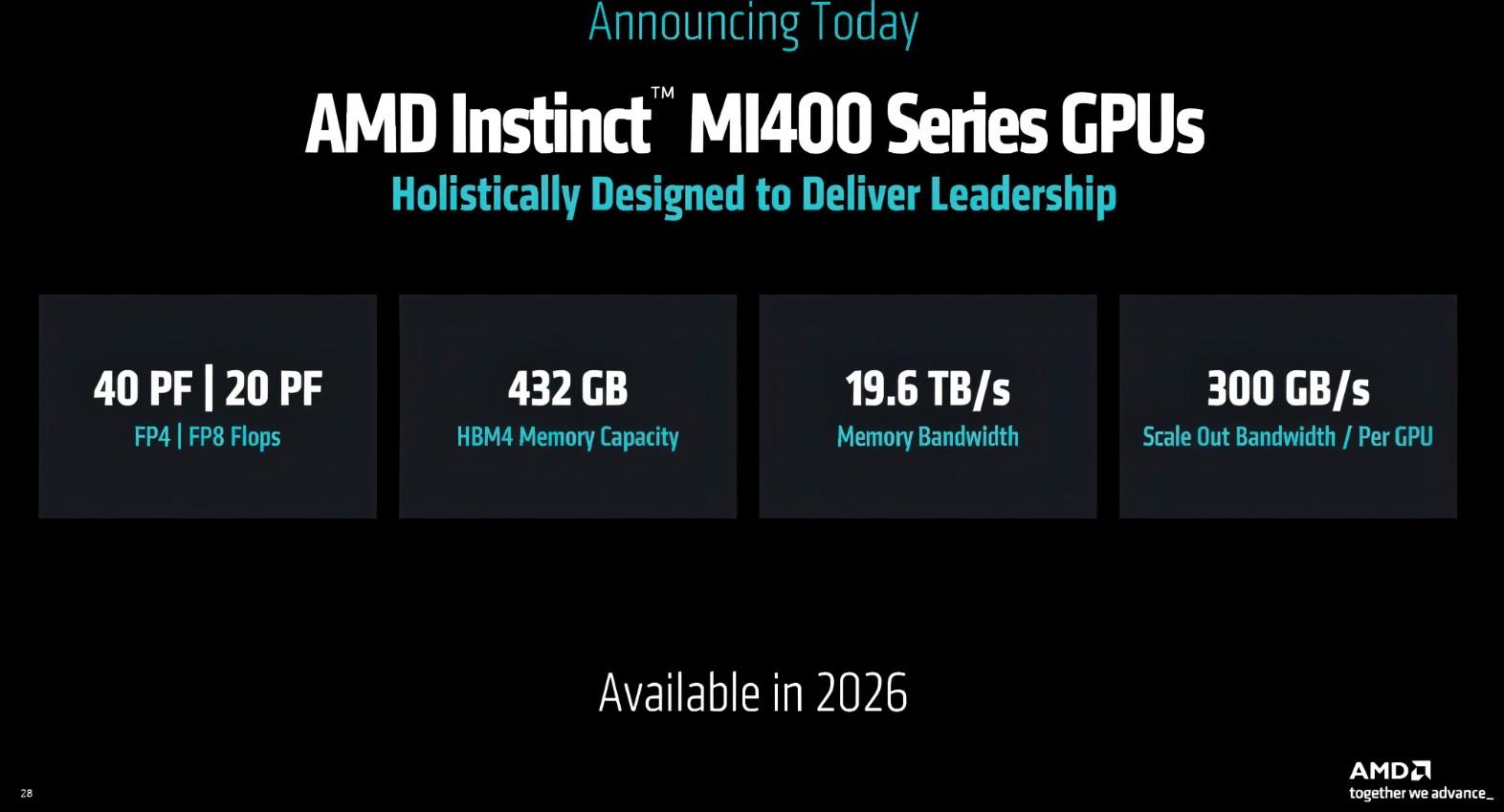

AMD a également confirmé l’arrivée de la MI400 Series en 2026. Basés sur une architecture CDNA-Next, ces accélérateurs intégreront jusqu’à 432 Go de mémoire HBM4, avec une bande passante atteignant 19,6 To/s — soit plus du double de celle des MI350X / MI355X. Vous l'aurez remarqué, une autre série, celle des MI500, est déjà évoquée pour 2027, bien qu’aucune spécification n’ait encore été arrêtée à ce stade.

| AMD Instinct | Architecture | Unités de calcul GPU / cœurs CPU | Mémoire | Bande passante mémoire | Peak TBP |

|---|---|---|---|---|---|

| MI400 | AMD CDNA-Next | ? | 432 Go HBM4 | 19,6 To/s | ? |

| MI355X | AMD CDNA4 (N3P+N6) | 256 / 0 | 288 Go HBM3e | 8,0 To/s | 1400 W |

| MI350X | AMD CDNA4 (N3P+N6) | 256 / 0 | 288 Go HBM3e | 8,0 To/s | 1000 W |

| MI325X | AMD CDNA 3 (N5+N6) | 304 / 0 | 288 Go HBM3e | 6,0 To/s | 1000 W |

| MI300A | AMD CDNA 3 (N5+N6) | 228 / 24 | 128 Go HBM3 | 5,3 To/s | 760 W |

| MI300X | AMD CDNA 3 (N5+N6) | 304 / 0 | 192 Go HBM3 | 5,3 To/s | 750 W |

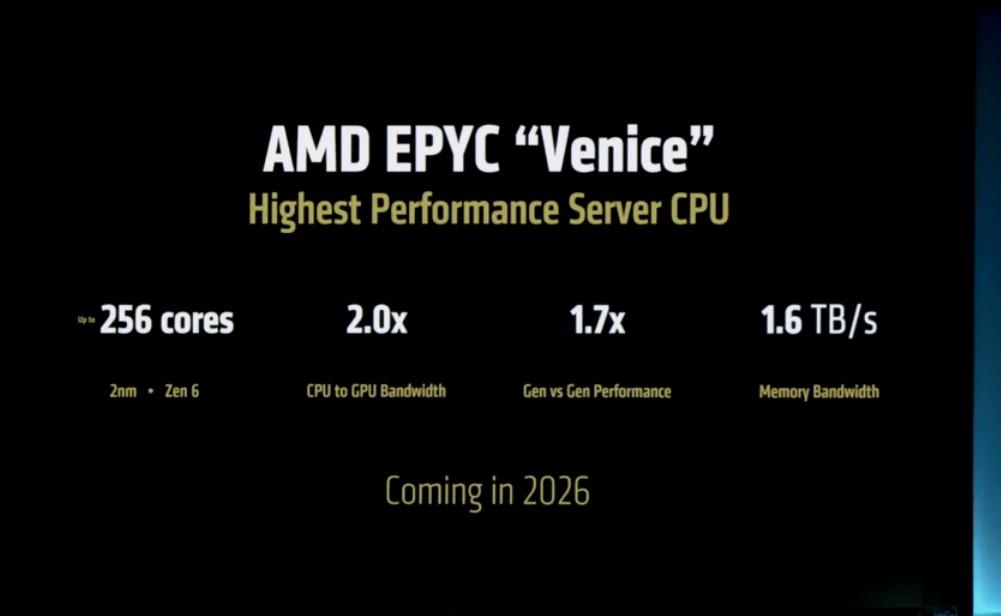

Du côté des CPU, AMD a parlé de ses prochaines générations EPYC. Prévue pour 2026, la gamme Venice, conçue en 2 nm, exploitera l’architecture Zen 6 et proposera jusqu’à 256 cœurs par socket dans sa version dense (Zen 6c), soit une augmentation de 33 % par rapport aux EPYC Turin actuels. AMD annonce également des gains de performances pouvant atteindre 70 %, sans préciser les charges de travail concernées — ce qui rend cette assertion vague.

La bande passante mémoire par socket serait plus que doublée : 1,6 To/s contre 614 Go/s aujourd’hui. Si les détails techniques manquent, on peut raisonnablement attribuer ce bond à l’intégration de modules avancés type MR-DIMM.

Pour 2027, AMD anticipe une nouvelle génération baptisée Verano. C'est la première mention officielle de cette série. Aucune information technique n’a encore filtré ; à voir si elle marquera le passage à l’architecture Zen 7.

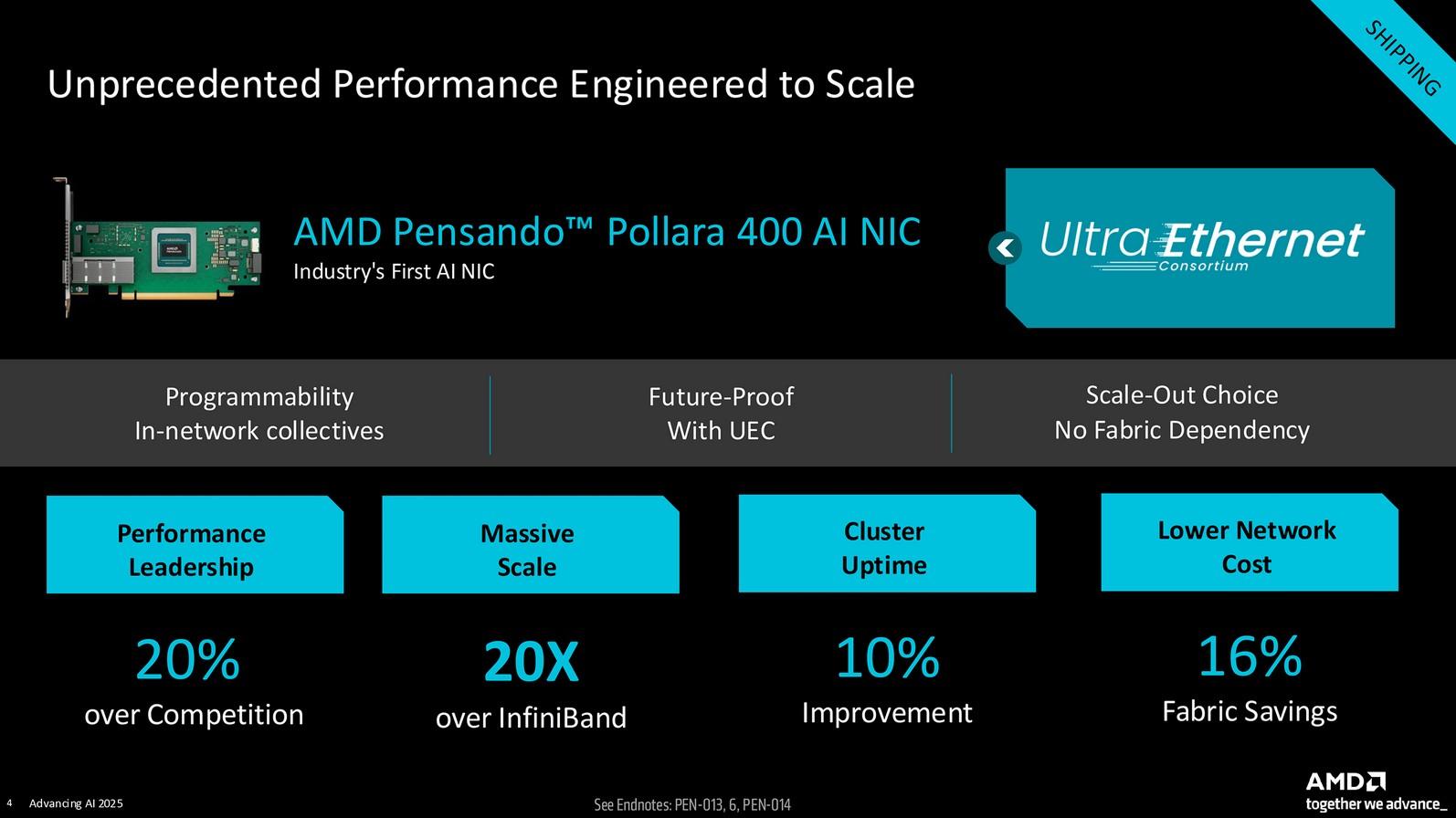

Pour ceux qui s'interrogent à ce sujet, quelques mots sur Pensado Pollara. Cela désigne la carte réseau éponyme dévoilée en octobre dernier, et conçue dans le cadre de l'Ultra Ethernet Consortium. À ce propos, l'UEC a officialisé sa spécification 1.0 le 11 juin. Si la Pollara plafonne à 400 GbE, AMD prévoit des systèmes Helios combinant processeurs EPYC Venice, accélérateurs Instinct MI400X et cartes réseau Pensando Vulcano à 800 GbE l'année prochaine. Et au cas où, NIC est l'acronyme de network interface card.

Ce tour d’horizon reste généraliste et non exhaustif. Pour approfondir certains aspects ou découvrir des produits en détail, n’hésitez pas à consulter les pages officielles d’AMD. Et si vous avez deux heures devant vous, le replay complet de l’évènement est disponible ci-dessous.

| Un poil avant ?TSMC prépare CoPoS : du wafer rond au panneau rectangulaire | Un peu plus tard ...Ryzen 5 5500X3D : un nouveau CPU AM4 |  |