Des bons gros CPU pour serveurs chez arm : les N1 et E1 |

————— 21 Février 2019 à 20h48 —— 14822 vues

Des bons gros CPU pour serveurs chez arm : les N1 et E1 |

————— 21 Février 2019 à 20h48 —— 14822 vues

Hasard du calendrier, la sortie de nouveaux design ARM coïncide à quelques jours près avec celle d'un projet d'émulation des binaires x86 sur Linux ARM. Linux qui est, rappelons-le, le principal OS sur ce segment. En effet, les Anglais concepteur de SoC efficients énergétiquement ont dévoilé hier deux plateformes dédiées à ces usages : les Neoverse N1 et E1.

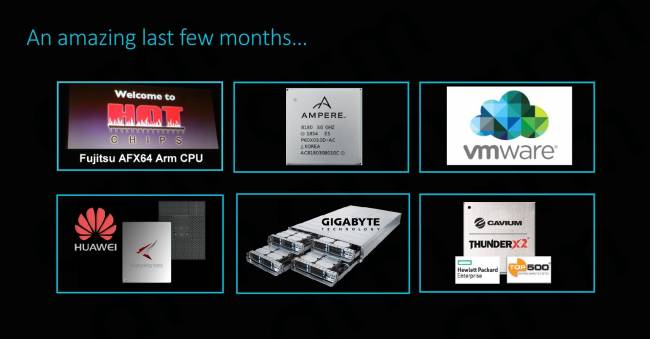

L'offre sur le segment serveur d'ARM s'est considérablement élargie ces derniers temps

Les N1 sont architecturés autour d'un CPU du même nom comportant une structure proche du Cortex A-76 dévoilé en 2018 : 7 nm, jeu d'instructions 64-bit ARMv8.2-A, 64 ko de cache L1D et L1I ainsi que 512 à 1024 ko de L2, tous deux pouvant contenir des données supportant la correction d'erreur. Côté ressource matérielle, on a droit à trois unités de calcul entier, deux unités SIMD 128-bit accompagnées de leurs confrères de chargement-rangement, le tout imbriqué dans un pipeline Out-of-Order de 11 étages. Un changement majeur par rapport à la version grand public réside dans la topologie d'organisation des caches en mesh via le CMN-600 Coherent Mesh Network qui n'est pas sans rappeler la solution proposée par Intel sur sa Scalable Platform. Notez que, comme à l'accoutumée avec ARM, la partie CPU est très réduite : sur la version à 512 ko de L2, il est question d'une surface de 1,2 mm² seulement, pas mal pour les coûts de production.

Bien que la gamme exacte de CPU n'ait pas été dévoilée, il a été question de modèles à 64 cœurs pour des fréquences allant de 2,6 à 3,1 GHz, le tout dans une enveloppe thermique de 105 W : en route vers la haute performance !

Le Neoverse E1 est plus timide : avec des caches L1 pouvant être de 32 ou 64 ko, un L2 facultatif entre 64 et 512 ko (toujours avec ECC), ce CPU est issu du Cortex-A65AE, un design conçu pour l'automobile autonome. Mais la grande nouveauté réside l'apparition du SMT à 2 voies, c'est à dire le dédoublement de certains composants pour faire mouliner deux cœurs logiques sur un cœur physique dans le but de continuer à exploiter les ressources de calcul du thread jumeau quand le premier est dans l'attente d'une donnée provenant de la mémoire. Issue d'un pipeline Out-of-Order à 10 étages, ce E1 se compare plutôt aux Cortex-A55, et est calibré pour une fréquence proche de 2,5 GHz tout en étant prévu pour être embarqué dans un design de référence à 32 cœurs. La cible est cette fois des serveurs relais orientés transmissions de données avec la 5G en ligne de mire : on reste quelque part liée à l'informatique embarquée ! (Source : WikiChip et AnandTech)

Windows ? En voilà une drôle d'idée pour ces cœurs next-gen !

| Un poil avant ?Les films sur Steam, c'est fini ! | Un peu plus tard ...Denuvo 5.6 de Metro Exodus et l'UWP de Crackdown 3 sont déjà tombés |  |