Samsung met au point des transistors de 3 nm : les MBCFET |

————— 15 Mai 2019 à 13h16 —— 16929 vues

Samsung met au point des transistors de 3 nm : les MBCFET |

————— 15 Mai 2019 à 13h16 —— 16929 vues

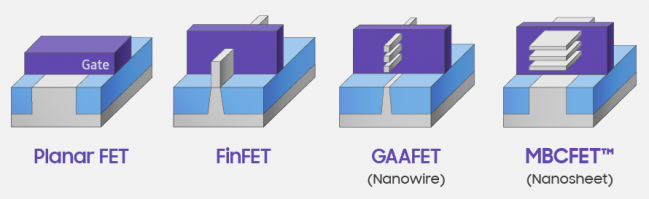

Nous l'avons vu récemment, l'industrie du semi-conducteur cherche à revoir le futur des transistors pour améliorer les performances de nos machines qui commencent à stagner légèrement de générations en générations. Un défi loin d'être simple qui demande de revoir une grosse partie de la fabrication, des outils de fabrication au transistor eux-même. C'est sur ce point que Samsung vient communiquer le fruit de ses dernières recherches en sortant une technologie des laboratoires et proposant une version alpha du PDK - Process Design Kit, l'ensemble des outils pour "choisir" le transistor à produire - d'une nouvelle génération : les MBCFET, technologie pouvant atteindre actuellement les 3 nm et marque déposée par le fondeur.

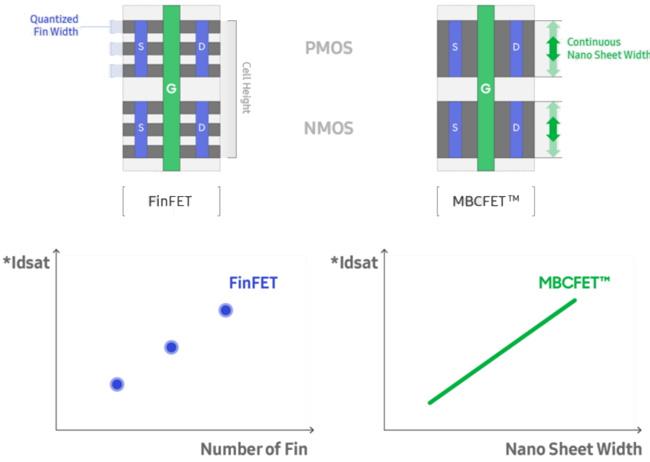

La technologie se distingue par une rupture de la jonction unique du canal qui caractérise les FET traditionnels pour faire place à un design par superposition de feuilles intégrée intégrée afin d'augmenter la surface de contact entre le canal et la grille. Arrivé au niveau de miniaturisation actuel, le canal est capable de conduire entre chaque feuille et la couche dopée principale vans contact physique proche, à 3 nm les transistors se rapprochant de plus en plus de la structure cristalline du silicium - en gros les atomes de chaque couches deviennent suffisamment proche pour émettre entre-eux. Une innovation qui permet deux points : l'augmentation de la surface de contact qui améliore l'efficacité et les performances des transistors et un système planaire qui est customisable sans changer d'outil de fabrication. Cela permet de réaliser des transistor au rapport consommation/performance beaucoup plus précis selon les besoins. Mais arrivant tout juste en version Alpha 0.1, nous ne sommes pas prêt de voir la technologie dans nos machines. (source : Anandtech)

| Un poil avant ?Comptoiroscope • 21:9 natif pour Rage 2 ! | Un peu plus tard ...Live Twitch • Après la rage, la peste ? |  |