TSMC trace sa route jusqu’à 2029 entre A13, N2U et stratégie Low-NA |

————— 23 Avril 2026 à 13h40 —— 418 vues

TSMC trace sa route jusqu’à 2029 entre A13, N2U et stratégie Low-NA |

————— 23 Avril 2026 à 13h40 —— 418 vues

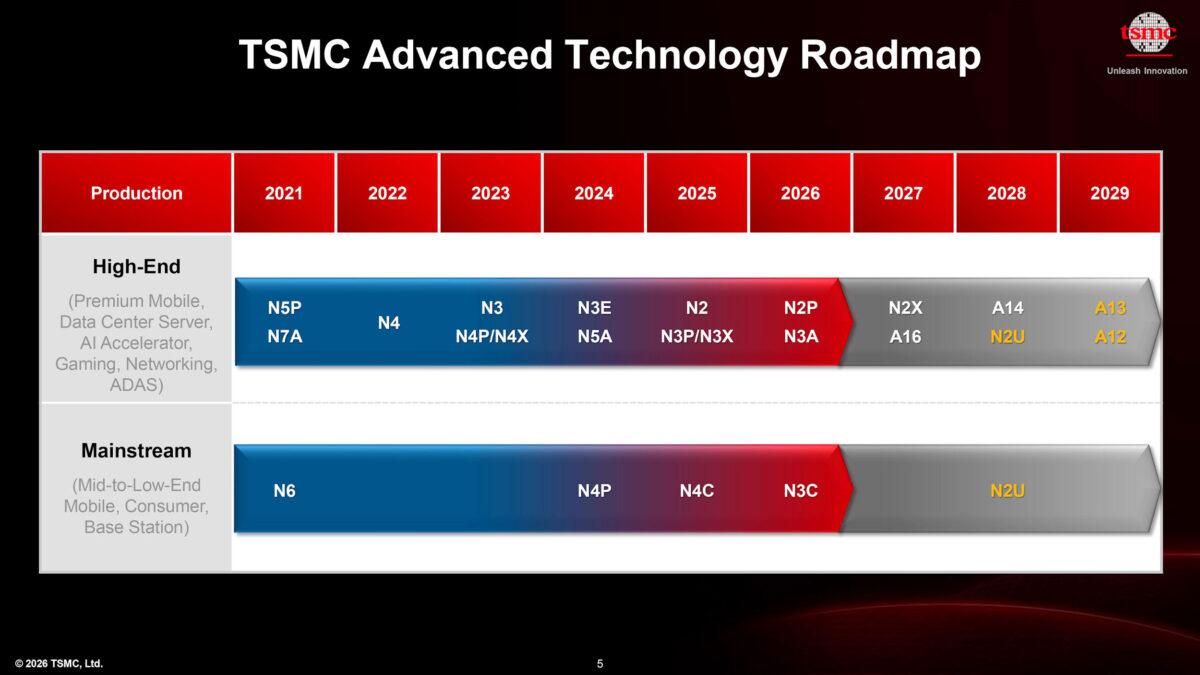

Dans le cadre du North America Technology Symposium 2026 à Santa Clara, TSMC a révélé sa feuille de route qui mène, presque, jusqu’à la fin de la décennie (la pécédente s'arrêtait à 2027). Les « nœuds étapes » ajoutés à l’itinéraire sont les procédés de classe 1,2 nm et 1,3 nm, baptisés A12 et A13, ainsi que le N2U, une extension du N2. Par ailleurs, si l’expression « ce n'est pas la destination qui compte mais le voyage » est souvent utilisée à tort et à travers, elle prend un certain sens ici. En effet, TSMC n’envisage pas de recourir à la lithographie EUV High-NA, qui marquerait une rupture majeure, mais d'en rester au Low-NA EUV pour le moment.

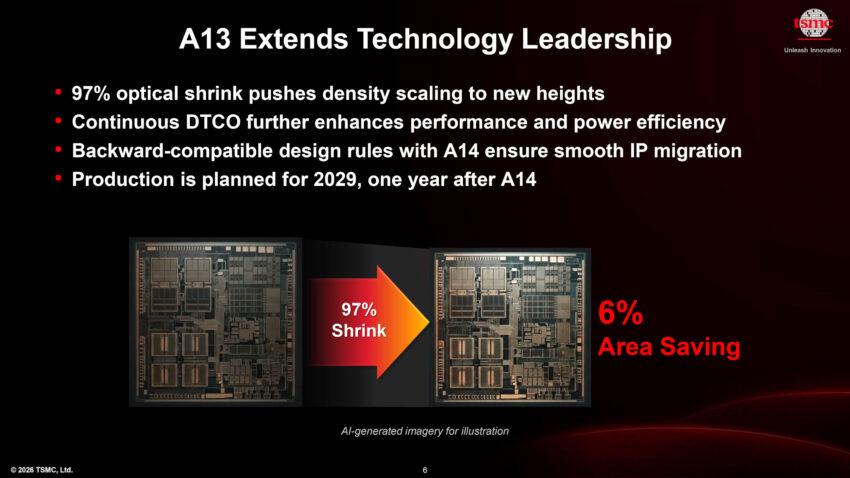

Concernant les nœuds de gravure, le communiqué et le tableau qui suit (pris chez Tom’s Hardware US) vous donneront un bon aperçu de leurs caractéristiques. L’A13 est décrit comme une version optimisée de l’A14. Il garantit une compatibilité totale avec les règles de conception de son prédécesseur, mais octroie un gain de surface de 6 %. L’A12 est aussi une évolution de la plateforme A14 intégrant une alimentation par l’arrière (backside power delivery) via la technologie Super Power Rail. Ces deux processus doivent servir aux puces conçues pour les charges de travail en IA et HPC ; tous deux sont prévus pour 2029.

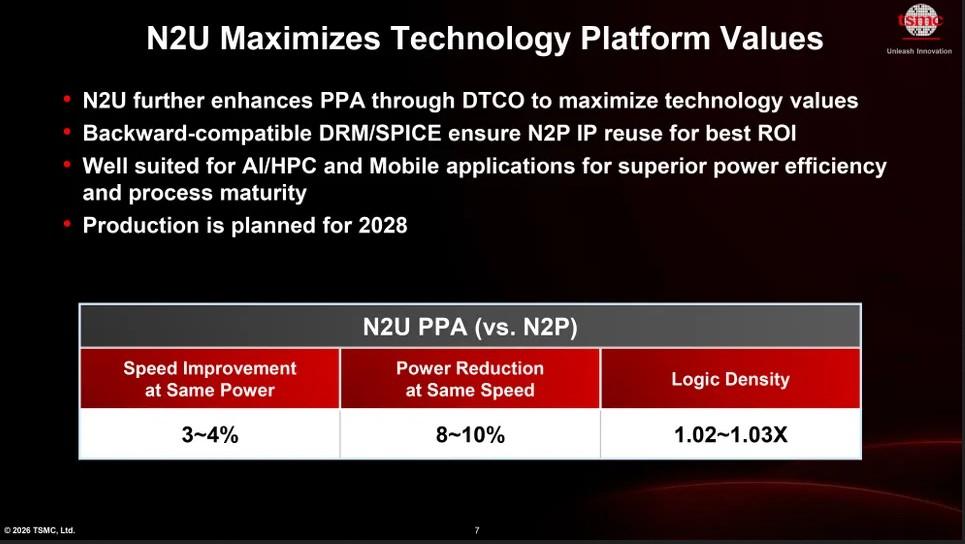

Le N2U s’inscrit comme une nouvelle variation au sein de la plateforme 2 nm. TSMC promet des gains modestes mais mesurables, avec 3 à 4 % de performances supplémentaires ou, à l’inverse, une baisse de la consommation de l’ordre de 8 à 10 % face au N2P. La densité logique progresse elle aussi légèrement, dans une fourchette de 1,02x à 1,03x. Industrialisation attendue en 2028.

Sur le volet packaging, TSMC indique déjà produire des solutions CoWoS exploitant 5,5 réticules, et vise une montée en gamme avec une version à 14 réticules d’ici 2028. À ce niveau, il deviendrait possible d’assembler une dizaine de gros dies de calcul accompagnés d’une vingtaine de piles HBM. L’étape suivante est déjà dans le viseur, avec des configurations au-delà de 14 réticules à l’horizon 2029, en parallèle du déploiement de la plateforme SoW-X capable de grimper jusqu’à 40 réticules. Dans le même temps, un empilement SoIC A14 sur A14 est attendu pour 2029, avec une densité d’interconnexion entre dies annoncée comme 1,8 fois supérieure à celle du SoIC N2 sur N2.

TSMC a également levé le voile sur plusieurs évolutions touchant à l’optique, à l’automobile et à certains procédés spécifiques. Sa solution COUPE, qui repose sur une intégration d’optique directement au niveau du substrat, est prévue pour une mise en production en 2026. L’entreprise avance à ce sujet un doublement de l’efficacité énergétique et une latence drastiquement réduite, jusqu’à dix fois inférieure à celle des approches modulaires classiques.

Côté automobile, le N2A marque l’arrivée du premier procédé à nanosheets de TSMC spécifiquement qualifié pour ce secteur. À puissance équivalente, des gains de performances compris entre 15 et 20 % sont évoqués face au N3A, avec une certification AEC-Q100 ciblée pour 2028.

Enfin, le procédé N16HV doit entrer en production dès 2026, avec en ligne de mire des applications comme les circuits de pilotage d’affichage.

| Comparaison des nœuds TSMC | A16 vs N2P | N2X vs N2P | N2U vs N2P | A14 vs N2 | A13 vs A14 | A12 vs A16 |

|---|---|---|---|---|---|---|

| Puissance | -15 % à -20 % | plus faible | -8 % à -10 % | -25 % à -30 % | ? | plus faible |

| Performances | +8 % à +10 % | 10,00 % | +3 % à +4 % | +10 % à +15 % | ? | plus élevées |

| Densité de puce | 1,07x à 1,10x | ? | ? | 1,2x | ? | plus dense |

| Densité logique | ? | ? | 1,02x à 1,03x | 1,23x | 1,06x | plus dense |

| Transistors | GAA | GAA | GAA | GAA 2e génération | GAA 2e génération | GAA 2e génération |

| Distribution de puissance | SPR | Alimentation front-side avec SHPMIM (?) | Alimentation front-side avec SHPMIM (?) | Alimentation front-side avec SHPMIM (?) | Alimentation front-side avec SHPMIM (?) | SPR |

| Production de masse (HVM) | 2027 | 2027 | 2027 | 2028 | 2029 | 2029 |

Notez que la densité de puce publiée par TSMC reflète une densité « mixte », composée de 50 % de logique, 30 % de SRAM et 20 % d’analogique.

Tout ce qui précède relève donc de la destination. Mais le plus intéressant est donc le moyen de s’y rendre, puisque TSMC ne mise toujours pas sur la lithographie EUV High-NA, comme cela avait déjà été le cas pour l’A16. Une stratégie opposée à celle d’Intel, pour qui le nœud 14A et les suivants reposeront sur des scanners High-NA (à partir de 2027–2028).

TH rapporte une déclaration de Kevin Zhang, vice-président du développement commercial chez TSMC : « Je peux vous dire que je suis impressionné par notre équipe R&D. Elle parvient encore à faire progresser le scaling technologique sans recourir au High-NA. Un jour, il faudra peut-être y passer, mais pour l’instant, nous sommes capables de tirer parti de l’EUV actuel sans franchir ce cap, qui, vous le savez, est extrêmement coûteux. »

Ainsi, plutôt que d’adopter les coûteux scanners EUV High-NA d’ASML (environ 350 millions d’euros l’unité), TSMC prévoit de s’appuyer sur ses machines EUV Low-NA, dont le coût est environ deux fois inférieur. Kevin Zhang ne détaille pas la manière dont les équipes œuvrent pour atteindre de tels niveaux de gravure avec ces outils, mais l’approche repose nécessairement sur le multi-patterning, un procédé consistant à effectuer plusieurs passes pour graver un motif sur une même couche. En multipliant les étapes d’exposition en Low-NA, l’entreprise estime ainsi pouvoir obtenir des résultats proches de ceux permis par une exposition High-NA.

Bien sûr, à terme, les limites du multi-patterning en Low-NA imposeront l’adoption des systèmes High-NA, y compris chez TSMC. Mais d’ici là, pour les générations actuelles et à venir, le fondeur estime pouvoir exploiter au maximum ses infrastructures Low-NA, avec un investissement nettement plus contenu que celui qu’exigerait une transition massive au High-NA.

Comme le rappelle TechPowerUp, si Intel fait aujourd’hui figure de pionnier dans l’adoption de l’EUV High-NA, l’entreprise occupait un rôle comparable à celui de TSMC lors du développement de son nœud 10 nm. À l’époque, plutôt que de basculer vers l’EUV Low-NA, qui aurait permis de lever une grande partie des difficultés — mais au prix de lourds investissements —, Intel espérait repousser les limites du DUV grâce au multi-patterning. Pour le résultat et le succès que vous connaissez. Pour la décennie qui se profile, les rôles semblent donc s’être inversés ; souhaitons au fondeur taïwanais une issue différente.

| Un poil avant ?Le Ryzen 9 9950X3D2 Dual Edition a désormais un tarif (MAJ) |