Intel Architecture Day • Sunny Cove contre-attaque |

————— 12 Décembre 2018

Intel Architecture Day • Sunny Cove contre-attaque |

————— 12 Décembre 2018

On ne vous fait pas de schéma, la plus grande annonce a été sans aucun doute la nouvelle architecture du géant bleu : Sunny Cove. Prévue dès le début pour être gravée en 10nm, elle sera dévoilée a priori sous la dénomination commerciale des puces Ice Lake, que l'on attend déjà depuis un bon moment. Si vous avez en tête le nom de Cannon Lake, sachez que pas un mot n'a été dit à son sujet, qui limitera son existence au seul i3-8121U, on suppose que le projet consistait à porter Skylake en 10nm avec le support de l'AVX-512 ; à moins qu'il ne s'agisse d'une solution pour limiter la casse lors des multiples tests de gravure de ce nouveau nœud.

![Si vous cliquez, vous cliquez. Skylake contre Sunny Cove [cliquer pour agrandir]](/images/stories/articles/cpu/intel-architectural-day-2018/skl-vs-sunnycove_t.png)

Niveau architectural, on a droit à de gros changements. Le cache L1 dédié aux données fait un bond de 50% en passant à 48 ko, et est désormais capable de supporter deux opérations de lecture et d'écriture simultanées, contre deux lectures pour une écriture précédemment. Notez que ce cache est resté bloqué à 32 ko depuis plus de 10 ans, c'est dire l'évolution. Le reste du pipeline suit cette évolution afin d’apporter un débit maximum à l'utilisateur. Pour rester dans les caches, le L2 sera également augmenté systématiquement par rapport à Skylake ; mais la quantité exacte reste inconnue - elle sera spécifique en fonction du modèle choisi, ce qui n'est pas sans rappeler la Scalable Platform. En outre, de nouvelles extensions du jeu d'instructions x86 seront à l'honneur avec cette prochaine architecture notamment au niveau de la cryptographie, ce qui permettra d'accélérer grandement la vitesse de compression de fichiers. D'autres instructions seront dédiées aux opérations de permutations et de comptage de bits (ce n'est pas ce que vous croyez chenapans) à l'intérieur d'un registre, un avantage non négligeable pour les compilateurs. Les détails complets sur l'ISA ne sont pas encore disponibles, d'autres gains étant attendus au niveau des instructions vectorielles par exemple, en sus de l'implémentation de l'AVX-512.

![Ultra bouzotron HD max def sunny cove 7 zip t [cliquer pour agrandir]](/images/stories/articles/cpu/intel-architectural-day-2018/sunny-cove-7-zip_t.jpg)

![Si vous cliquez, vous cliquez. kaby lake 7 zip t [cliquer pour agrandir]](/images/stories/articles/cpu/intel-architectural-day-2018/kaby-lake-7-zip_t.jpg)

Temps de compression d'une archive inconnue, Sunny Cove à gauche, Kaby à droite. Les fréquences (inconnues) sont identiques, de même pour le nombre de cœurs.

Ce n'est pas la seule évolution : si Sunny Cove conserve 4 ports dédiés aux micro-opérations effectuant des calculs, tous sont mis à niveau pour offrir plus de flexibilité, avec le renforcement des opérations permettant de réorganiser les bits au sein d'un registre (shuffle), d'un calcul d'adresse utilisé pour diverses optimisations (LEA, Load Effective Address), et des améliorations au niveau des multiplicateurs. Des améliorations moins visibles seront également de la partie, comme un cache plus gros des micro-opérations, un prédicteur de branchement toujours plus malin et un cache de niveau 2 pour le TLB (celui de la table des pages) agrandi lui aussi. Au passage, la latence de certaines instructions comme la division entière diminue, on attend avec impatience de voir le résultat sur des tests en conditions réelles. On citera également le passage d'adressage linéaire 48-bit (correspondant grosso modo à l'espace d'adressage virtuel pour nos bouzins) à 57-bit, et "seulement" 52-bit pour l'adressage physique, soit de quoi supporter 4 Po de RAM. Même avec des modules Optane, il y a de quoi voir venir !

![Cliquédélique ! Les plans pour le futur ! [cliquer pour agrandir]](/images/stories/articles/cpu/intel-architectural-day-2018/sunnycore-roadmap_t.png)

Non, "Next Mont" n'est pas "Next Month" !

Comme nous vous l'annoncions dans l'introduction, aucune date plus précise que "2019" n'a été dévoilée, il faudra donc se contenter des informations architecturales. Cela est néanmoins rassurant, un an étant le délai typique d'optimisation du rendement d'un procédé et non sa mise en production (qui elle dépasse les 2 années) : il semblerait bien qu'Intel ait fini par trouver son chemin parmi ses difficultés techniques. Au registre des mauvaises nouvelles, les correctifs de Spectre 1 restent logiciels uniquement, bien que de multiples recherches soient en cours à ce sujet et que Jim Keller nous a assuré que la sécurité est désormais une contrainte formelle lors de la conception de nouvelles puces.

![Enlarge your pe...icture La plateforme de démonstration de Sunny Cove [cliquer pour agrandir]](/images/stories/articles/cpu/intel-architectural-day-2018/sunny-cove-test-platform_t.jpg)

Une plateforme de test Sunny Clove

La palme de la nouveauté la plus surprenante de ces présentations revient sans conteste à Fiveros. Si le nom provient du grec "terrible", la puce est un OVNI dans le domaine de l'architecture x86 traditionnelle. Commençons par sa configuration : un pentacore. Qu'est-ce qu'ont bien pu prendre les ingénieurs pour arriver à un nombre impair ? Réponse simple : ils ont sorti leur ARM : cette configuration se décompose en 4+1, quatre cœurs basse consommation (Atom) pour un cœur hautes performances (Sunny Cove), ce dernier étant laissé dans un état de veille profonde (proche de l'état ACPI C6) lorsqu'aucune tâche ne lui est confiée. Cela rappelle énormément la technologie big.LITTLE chez les anglais d'ARM, et pour cause : le principe est identique ! Seconde particularité, et non des moindres : la puce est une puce 3D.

![Ultra bouzotron HD max def Empiler toujours plus de couches ! [cliquer pour agrandir]](/images/stories/articles/cpu/intel-architectural-day-2018/foveros-slide_t.jpg)

Notez la différence avec un Interposer à la AMD : ici, le die du dessous est actif

Gardons nos réserves, il ne s'agit pas de la 3D au sens mathématique du terme ("on grave ce que l'on souhaite dans l'espace") mais plus un 2,5D, car Foveros est composé de 2 dies. Celui du dessous semble remplacer le chipset avec la gestion des entrées-sorties ainsi que la gestion mémoire, et sera gravé en 22 nm (oui oui, ça existe encore chez Intel !). L'ensemble est ainsi une suite logique à l'EMIB, technologie dans laquelle les pucelettes étaient côte à côte au lieu de s'empiler. Les cœurs, par souci d'efficacité et de dissipation thermique, seront eux placés sur une puce secondaire soudée au-dessus, elle en 10 nm sous architecture Sunny Cove.

Notez que cet empilement provoque des difficultés de dissipation thermique encore jamais rencontrées. Jim Keller nous a avoué lors de la séance de questions/réponses que si les package 3D étaient certes porteurs de promesses, cela est à mettre en relation avec une finesse de gravure atteignant déjà la capacité de chauffer le silicium plus qu'il ne soit possible pour lui de dissiper. Comme souvent , tout sera l'affaire d'un compromis !

Ce demi-bout de silicium dans la main, c'est ça le Foveros, et le monsieur qui le tient, c'est Raja Koduri, à la tête de la division architecture

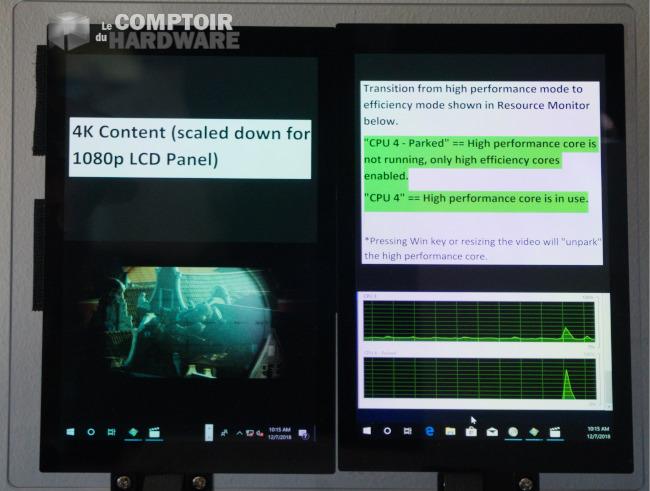

Au-dessus de tout ça, on retrouvera des puces mémoires pour un résultat d'une densité remarquable. Avec une taille de 12x12mm, ce SoC viendra concurrencer directement le Snapdragon 8cx à peine annoncé, si tant est que les partenaires suivent. Notons que la démo montrait un décodage de vidéo en 4K downscalé en 1080p de manière totalement fluide, ce qui est de très bon augure pour une intégration dans une tablette ou un téléphone. Un nouvel essai dans le domaine de l'ultra-mobilité ?

![Visionner en grand sur un magnifique pop-up La puce Foveros, planquée sous son ventirad [cliquer pour agrandir]](/images/stories/articles/cpu/intel-architectural-day-2018/foveros-package_t.jpg)

La plateforme Foveros sous (presque) toutes ses coutures

![Ne pas appuyer ici Un meilleur profil que Pascal, cette Foveros ! [cliquer pour agrandir]](/images/stories/articles/cpu/intel-architectural-day-2018/foveros-side_t.jpg)

Ici, le menu démarrer a été actionné au moment du pic du graphe du bas : l'ordonnanceur a réveillé le gros cœur. Pendant ce temps, la lecture 4K continue sur les 4 petits restants.

|

|

| Un poil avant ?Quel ventirad pour 32 coeurs sur TR4 ? | Un peu plus tard ...Creative Sound BlasterX AE-9 : une carte son pour vous faire roucouler |  |

| 1 • Préambule |

| 2 • |

| 3 • Gé Pé Hu : Xe et Gen11 |

| 4 • De la mémoire Optane et des gammes serveurs |

| 5 • IA : des solutions logicielles |

| 6 • FPGA : 10 nm également |

| 7 • Conclusion |