La plateforme d'un EPYC Genoa pourra être gavée de DDR5 ! |

————— 11 Décembre 2021 à 15h40 —— 13713 vues

La plateforme d'un EPYC Genoa pourra être gavée de DDR5 ! |

————— 11 Décembre 2021 à 15h40 —— 13713 vues

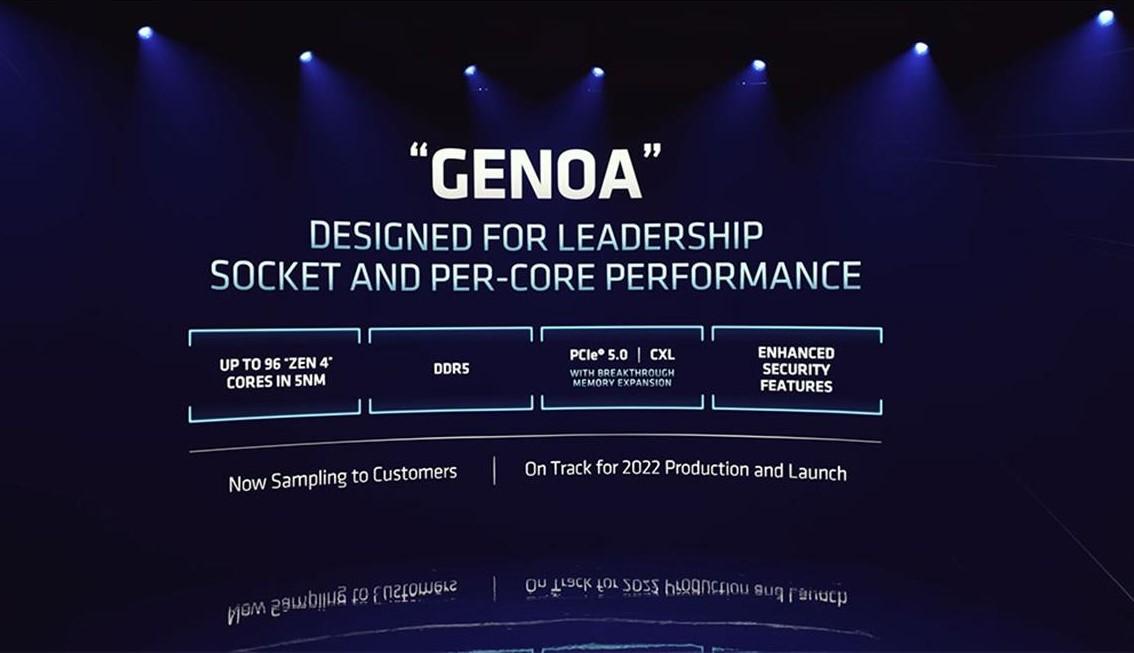

Genoa avec Zen 4 et 5 nm, c'est pour bientôt. AMD a déjà officialisé bon nombre d'informations à propos de la succession des EPYC Milan, comme sa compatibilité DDR5 et PCIe 5.0, ainsi que le nouveau plafond de 96 coeurs pour cette gamme ! Récemment, de nouveaux ajouts par les développeurs d'AMD aux pilotes Linux, afin de préparer cet environnement au support de la DDR5 et LPDDR5, ont aussi révélé que la quantité de canaux mémoire sera augmentée de 50 % ! En effet, le contrôleur mémoire d'un EPYC Genoa possédera 12 canaux, contre 8 auparavant.

L'info ne permet pas encore de savoir combien de DDR5-RDIMM ou DDR5-LRDIMM pourront être utilisés sur une plateforme, mais une autre rumeur suggère que Genoa pourra gérer jusqu'à deux modules mémoire par canal. Un EPYC Milan actuel peut être associé avec un maximum de 16 modules DDR4, la plus grosse capacité supportée par module est de 256 Go et la capacité totale par CPU est de 4 To. En effectuant un calcul identique pour Genoa, cela donnerait un plafond de 6 To. Toutefois, avec les modules DDR5 de 512 Go annoncés par Samsung cet été et qui sont d'ores et déjà supputés compatibles avec Genoa, le bruit court désormais qu'il sera possible de planter pas moins de 12 To de DRAM par socket ! La rumeur en question précise aussi que le contrôleur mémoire de Genoa pourra gérer jusqu'à de la DDR5-5200 et l'installation de 24 modules de la plus grosse capacité obligera à se limiter à de la DDR5-4000.

En tout cas, l'offre d'AMD sera visiblement toujours plus monstrueuse et la lutte avec les Sapphire Rapids s'annonce déjà bien intéressante, on en envierait presque les pros ! Certes, la bataille semble un peu inégale sur le papier, puisque l'alternative d'Intel devrait une nouvelle fois offrir moins de cores, avec un plafond toujours inférieur à celui de Milan aujourd'hui, et le nombre de canaux DDR5 sera en principe de 8 « seulement ». Par contre, les futurs Xeon seront supplémentés de mémoire HBM on-package, sans aucun doute une réponse au 3D V-Cache d'AMD, qui pourrait d'ailleurs peut-être aussi être proposé avec Genoa, comme AMD l'a fait avec les derniers EPYC Milan-X. Accessoirement, n'oublions pas que Bergamo viendra compléter Genoa un peu plus tard avec une variante Zen 4c et des EPYC jusqu'à 128 coeurs !

Dans cette lutte pour la suprématie dans les datacenters et les superordinateurs, Intel devrait néanmoins avoir l'avantage d'être le premier sur le terrain, les Sapphire Rapids (tout de même bien en retard) devant montrer la couleur de ses tuiles début 2022, tandis que l'on ne sait pas encore quand débarquera Genoa, bien que des échantillons ont en principe déjà été distribués aux clients d'AMD pour validation. (Source)

| Un poil avant ?Ocarina of Time sous Unreal Engine 5, vous voulez voir ? | Un peu plus tard ...Peu de cartes graphiques Arc Alchemist prévues |  |