Samsung dégaine son Cortex A15 |

————— 04 Décembre 2011 à 01h02 —— 11553 vues

Samsung dégaine son Cortex A15 |

————— 04 Décembre 2011 à 01h02 —— 11553 vues

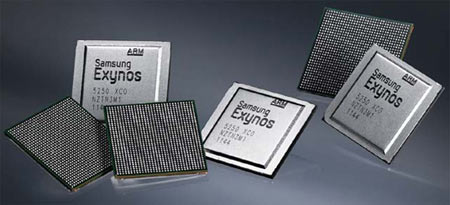

Samsung, un des concurrents énergique des Tegra3, Qualcomm et tutti quanti, vient d'annoncer son son nouveau CPU de la gamme Exynos. Il est le premier à être architecturé autour d'un CPU ARM Cortex A15 dual core et d'une puce graphique nouvelle venant de PowerVR, cette dernière saura rappeler des souvenirs aux geeks des années 2000 !

Concrètement, le modèle du jour, l'Exynos 5250, est capable de bombarder 14 milliards d'instructions par seconde à 2 GHz (attention ce sont des DMIPS), quasiment le double de ce que le Cortex A9 à 1.5 GHz pouvait donner de son côté, soit 7500 DMIPS. Ce n'est pas tout puisque la bande passante mémoire est doublée avec 12.8GB/s. Quant à la puce graphique, elle peut afficher jusqu'au 2560x1600, et est presque 4 fois plus puissante que celle embarquée avec le Cortex A9. L'Exynos 5250 a été gravé en 32nm utilisant la technologie High Metal k, il n'est qu'au stade du sampling, et sa production de masse est prévue pour le second trimestre 2012. Ca s'annonce chaud pour les tablettes !

| Un poil avant ?50 CPU pour Battlefield 3, mais guère plus hein.... | Un peu plus tard ...Le caméléon embauche, avez-vous le profil ? |  |