Mitigations hardware des spectres : AMD s'explique |

————— 04 Juin 2019 à 09h37 —— 19134 vues

Mitigations hardware des spectres : AMD s'explique |

————— 04 Juin 2019 à 09h37 —— 19134 vues

Ces deux dernières années ont été lourdes en failles, avec toujours une même origine : l'exécution spéculative. Si cela vous branche, notre dossier sur l'architecture des CPU pourra vous aider à y voir plus clair. Dans les grandes lignes, lorsque le processeur arrive à une instruction lui demandant de sauter conditionnellement à un autre endroit, il faut calculer le résultat de la condition avant de sauter : logique. Sauf que, pour aller plus vite, le processeur va supposer à l'avance le résultat, continuer son exécution en conséquence et, lorsque le résultat est disponible, valider ou invalider le travail effectué. Ce mécanisme s'avère très efficace dans le cas des boucles, c'est pourquoi il a toujours été conservé dans les modèles actuels... mais n'avait pas été pensé sous l'axe de la sécurité : l'invalidation du travail n'est pas totale, ce qui fait que des traces restent dans certains endroits, traces qu'il est possible de récupérer par un autre processus, fait connu sous le nom de canal auxiliaire.

À la conception de Zen, AMD annonce avoir pris soin de revoir son architecture pour éviter au maximum ce genre d'attaques. Si cela semble évident, la réalité est plus complexe : vider un cache peut être une opération longue, illustrant le fait que performances et sécurité s'opposent en règle générale. Mais le plus simple reste encore de ne pas toucher le cache : et c'est ce qui est employé dans le TLB. Ce cache sert schématiquement à garder proche du CPU les dernières adresses mémoires utilisées, que ce soit par le noyau (des espaces protégés) ou par l'utilisateur. C'est là qu'AMD a été prudent : depuis Zen, tous les bits de permissions sont également présents, ce qui permet au CPU de faire les vérifications de droit d'accès avant tout chargement (spéculatif ou non !), limitant ainsi le risque de failles. Pour les failles liées à l'Hyperthreading - nommé SMT chez AMD - un bit indique également quel cœur logique a créé la zone mémoire ; ce qui permet de cloisonner les processus même en cas de partage quasi total des ressources.

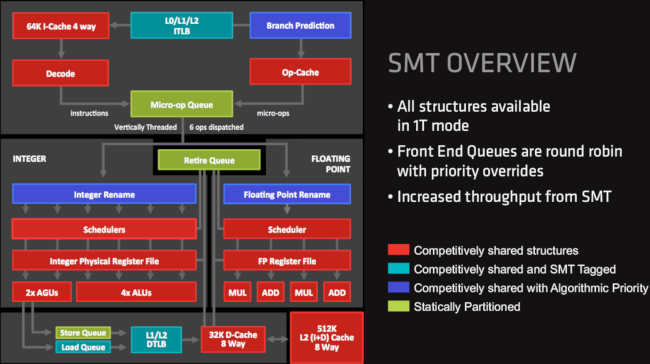

Cloisonnement entre les threads d'un même cœur : les unités de calcul pures sont partagées, les autres sont soit dupliquées (partitionnement statique) soit partagées avec un bit d'appartenance ou selon un algorithme permettant d'optimiser la rapidité d'exécution - le principe même du SMT.

Le TLB n'est pas le seul à bénéficier de cette structure : dans le cas du SMT, très largement présent sur Zen, et encore davantage sur Zen2, les structures de stockage des données sont soit partagées avec un bit d'appartenances, soit statiquement, ce qui revient à dire que deux caches sont présents, chacun étant assigné à son cœur. Sans surprise, les queues de stockages des valeurs, le DTLS ainsi que les caches d'instructions permettant au fonctionnement Out-of-Order du bouzin sont cloisonnés : c'est naturel et c'est tant mieux !

La gestion matérielle des erreurs est également très fine : si quelque chose se passe mal lors de l'exécution spéculative (par exemple, une adresse mémoire n'est pas valide), suivant la faute, aucune donnée n'est transférée vers les instructions suivantes, mettant fin à cette partie de la spéculation. Logique ? Pas nécessairement lorsque le CPU est construit : il est plus rapide chez Intel de faire toute l'exécution, puis ensuite de regarder les erreurs effectuées, c'est ce qui a mené à une branche de Spectre. Par ailleurs, toutes les fautes ne sont pas des erreurs : certaines servent à geler le processus pour du debug, ou peuvent être un overflow, parfois (mais très rarement) utilisé intentionnellement dans les programmes.

Notons que ce ne sont pas les seuls mécanismes de spéculation utilisés dans l'architecture Zen (il en existe pour les calculs flottants ou les chargements mémoires, mais ceux-ci sont également cloisonnés pour éviter toute fuite de donnée). Cependant, AMD ne précise aucune mesure comme étant spécifique à Zen2 : qu'il s'agisse d'un coup de bol d'un processeur bien construit à la base ou d'une attention particulière de la firme à la sécurité, on ne peut qu'apprécier le travail fourni, qui semble par ailleurs payer avec un succès commercial. Reste à voir si, avec la démocratisation d'EPYC en entreprises, les chercheurs n'iront pas regarder d'un peu plus près l'agencement interne et trouver des failles critiques chez les rouges...

| Un poil avant ?GIGABYTE annonce un SSD PCIe 4.0 tout cuivré | Un peu plus tard ...Des switch... étranges dans un vieux générateur HP ! |  |