La guerre de succession du 7nm a déjà démarré |

————— 23 Janvier 2020 à 16h08 —— 19467 vues

La guerre de succession du 7nm a déjà démarré |

————— 23 Janvier 2020 à 16h08 —— 19467 vues

En parallèle des courses à la puissance chez les fondeurs de semiconducteurs se déroule également une réflexion sur les évolutions à venir autres que l’amélioration de la finesse de gravure des composants en silicium. En effet, pour poursuivre la courbe d’augmentation de performances, il va falloir revoir la conception des transistors et des circuits, soit en passant par des design 2.5D ou 3D, par exemple en multipliant les chiplets — la conception des puces de grandes tailles avec une finesse de gravure faible étant trop coûteuse ; soit en changeant complètement le type de transistor utilisé. Et pour passer au 5 nm voire au 3 nm, les possibilités sont multiples et ravivent la concurrence entre les différents fondeurs.

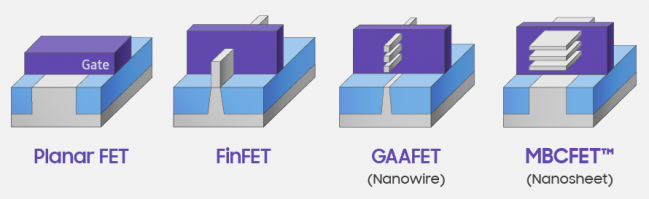

Pour une telle transition, la solution la plus probable à terme est de donner sa retraite aux transistors finFET pour passer aux GAA FET ou aux MCBFET, comme ceux en cours d’étude et de réalisation chez Samsung. Deux technologies qui permettent de repousser légèrement les lois de la physique qui bloquent petit à petit la miniaturisation de nos puces électroniques. Mais voilà, ces designs sont toujours bloqués à des phases d’approbation et de validation, ce qui ne donne pas toujours les résultats escomptés, d’autant plus que les GAA FET sont considérés comme transitoires par Samsung, qui mise principalement sur les nanosheet, plus performants... mais dont il est difficile de prévoir une arrivée en préproduction avant fin 2021.

C’est donc ici que va très probablement commencer une nouvelle guerre sur le sujet, ou tout du moins la mettre totalement en avant. Au vu des surfaces actuelles des composants, l’évolution basée sur la taille va commencer à montrer ses limites, ce qui signifie que l’action va basculer sur ce qui est encore parfois trop souvent mis de côté : l’optimisation, le design et les matériaux. Il est probable qu’une ère de la nanotechnologie se ferme, ou plutôt naisse enfin : les avancées seront surtout sur la refonte des transistors, des interposers et des puces en 3 D. Mais un tel futur ne va pas apparaître du jour au lendemain et la course a commencé avec le 7 nm. Si TSMC préfère toujours jouer sur le scaling des finesses jusqu’au 3 nm pour éviter de se laisser distancer et faire vendre ce procédé, Samsung préfère jouer la prudence et de terminer le développement de ses puces basées en GAA FET, très probablement histoire de vendre de meilleures performances. Cela va donc ajouter de la poudre dans la bataille du 7 nm, où les fabricants vantent déjà les différences entre les procédés de gravure. Il faudra donc être patient et comprendre que dans les années à venir, il sera encore plus difficile de comparer l’efficacité et la puissance des puces uniquement par leur finesse de gravure, les paramètres incriminés devenant plus nombreux, et ce, dès à présent. (source : SemiEngineering)

En attendant, l'avenir sur qui gagnera la guerre est toujours dans les bouliches de cristal

| Un poil avant ?Zbox Magnus EN92080V : rikiki, mais avec des muscles taillés en Core i9 et GeFORCE RTX | Un peu plus tard ...Le H510 détecté, premier chipset pour Rocket Lake-S |  |