Des SoC adaptables chez Xilinx |

————— 20 Mars 2018 à 15h35 —— 12174 vues

Des SoC adaptables chez Xilinx |

————— 20 Mars 2018 à 15h35 —— 12174 vues

La mode CPU en ce moment est au puces multi-modules. Entre EPYC composé de quatre dies Zeppelin et l'EMIB capable de relier différents modules chez les bleus, on peut dire que cette technologie paraît avoir de beaux jours devant elle. Xilinx, boîte américaine pionnière dans le domaine des FPGA, suit le mouvement, et annonce une nouvelle gamme de produits, connus sous le nom de Projet Everest.

Un brin français dans l'âme cette architecture ?

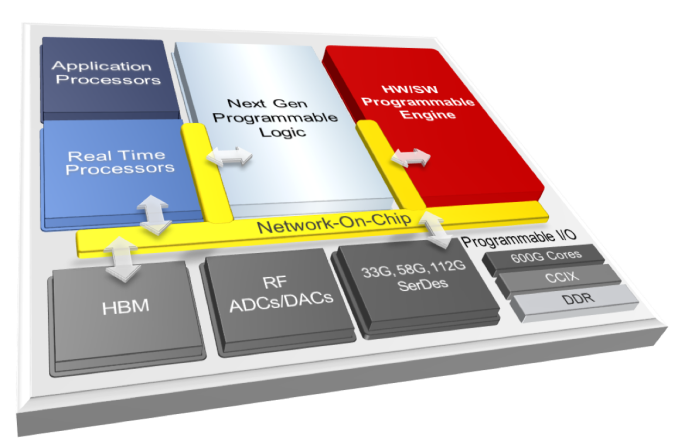

Contrairement aux CPU classique, il s'agirait d'ACAP (Adaptive Compute Acceleration Platform, ou plate-forme adaptative d'accélération en bon vieux françois). L'idée est d'intégrer sur un même package des accélérateurs divers tels des encodeur/décodeurs de radiofréquences, des entrées/sorties programmables ainsi qu'une tripotées d'unités spécialisées dans le traitement du signal, le tout saupoudré de HBM. Tout ce beau monde serait relié par un interconnect maison à une sorte d'FPGA amélioré, capable de se reconfigurer en quelques millisecondes, est serait gravé en 7 nm par TSMC.

Mais pourquoi cela ? L'idée serait d'aller au-delà de la scission habituelle CPU-GPU en offrant une puissance de calcul plus flexible, adaptable en fonction de la tâche à effectuer, réalisant ansi un "accélérateur universel". Bien que l'annonce soit à l'heure actuelle davantage un communiqué sur l'avancement du projet (qui a parlé de rassurer les actionnaires ?), ce dernier pourrait bien fleurir, particulièrement dans le domaine professionnel où ce type de produit trouve tout son sens. S'il est encore bien trop tôt pour parler prix, la puce en version finale serait à prévoir pour 2019. (Source : AnandTech)

| Un poil avant ?Comptoiroscope • Devil May Cry HD Collection : framerate stable ? | Un peu plus tard ...Comme pressenti, le Ray Tracing arrive pour de bon dans la vie des joueurs |  |