Les specs de la mémoire HMC entrent en phase de finalisation |

————— 03 Avril 2013 à 19h30 —— 14834 vues

Les specs de la mémoire HMC entrent en phase de finalisation |

————— 03 Avril 2013 à 19h30 —— 14834 vues

Comme nous vous le disions hier, la fin de la loi de Moore est proche, au moins pour AMD et, dans une moindre mesure, son chef des architectures GPU John Gustafson. Mais il existe bien des façons d'envisager l'avenir, comme par exemple, les processeurs construits par couches successives, là où il n'y a pour les processeurs actuels qu'une surface en 2D. L'intérêt étant qu'il devient alors possible de multiplier les cores très facilement, et d'autant plus simple encore de les connecter entre eux.

Si ce n'est qu'une voie possible pour la recherche, pour continuer à augmenter les performances des processeurs, il est possible que ce ne soit pas les CPU qui soient les premiers à faire le saut vers la tridimension. En effet, le HMCC ou Hybrid Memory Cube Consortium, qui réunit des poids lourds comme Samsung, Hynix, Micron et Microsoft, mais compte aussi des membres comme ARM, HP et IBM ainsi que Xilinx et Open-Silicon, a publié la version 1 des spécifications de la mémoire éponyme (HMC donc), avec un peu de retard puisque la deadline du consortium avait auparavant été fixée à fin 2012.

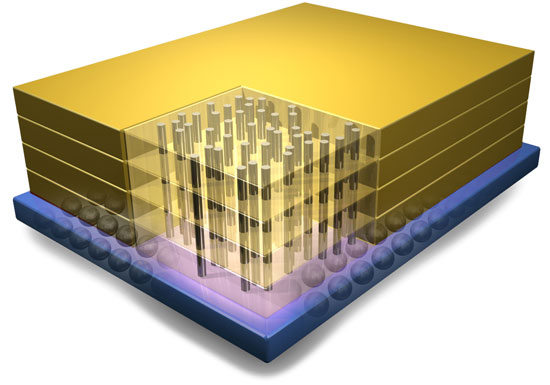

Il s'agit donc là d'un vrai pas en avant vers la commercialisation de tels modules de RAM. Leur structure est similaire aux hypothétiques processeurs 3D : il s'agit de couches empilées les unes sur les autres et connectées entre elles, ici avec une technologie appelée TSV pour Through-Silicon Vias ("routes à travers le silicium").

Micron avait déjà fait la démonstration d'un de ses prototypes en 2012, une mémoire qui débitait du 128Go/s, un nombre dix fois supérieur à ce dont est capable la DDR3. Mais ce n'était pas son seul avantage : elle consommait aussi 70% d'énergie en moins lors d'un transfert de données, ce qui a évidemment fait tourner quelques têtes du côté des constructeurs de machines mobiles. Mais compte tenu des prix inhérents à cette technologie, Micron avait déclaré à l'époque s'adresser surtout au HPC (High Performance Computing).

La version 2.0 des spécifications de la mémoire HMC est attendue pour début 2014. (Source Bit-tech)

| Un poil avant ?Et Asus officialisa sa GTX 670 DirectCU Mini | Un peu plus tard ...Bon plan: Red Orchestra 1 et 2 + Killing Floor à partir de 2,50€ |  |

|

j'espere qu'ils vont la plugger directement sur le die. Comme ça, debits monstrueux et composants miniaturisés niveau carte mere. Il ne manque plus qu'a intel de faire des cpus masivement parallelisés (il serait temps !!!), et l'informatique hpc passe un nouveau cap...