Hard du Hard • La Course aux Nanomètres - Partie 3 |

————— 19 Décembre 2023

Hard du Hard • La Course aux Nanomètres - Partie 3 |

————— 19 Décembre 2023

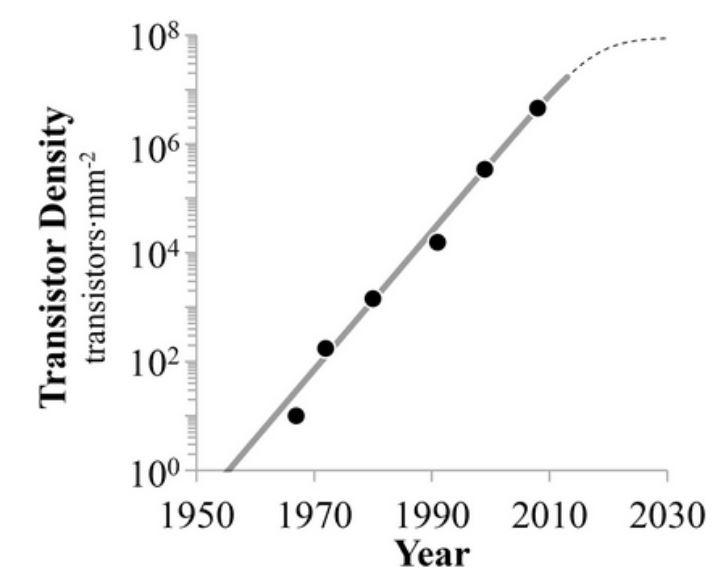

La loi de Moore, du nom du fondateur d'Intel Gordon Moore, stipule que l'industrie double le nombre de transistors présents sur une puce de microprocesseur tous les deux ans. Cette loi n'est pas une loi physique, mais une observation de l'industrie de l'électronique à ses débuts : en réalité, en 1965, on doublait les transistors sur les puces tous les 18 mois.

Si ce n'est pas une loi physique, c'est un argument économique : les investissements massifs nécessaires pour faire progresser la technologie doivent se justifier par des gains en productivité. Et doubler le nombre de transistors pour (globalement) le même prix de matière première, c'est plutôt bien ! Venez les copains, ça vaut le coup d'y investir dedans.

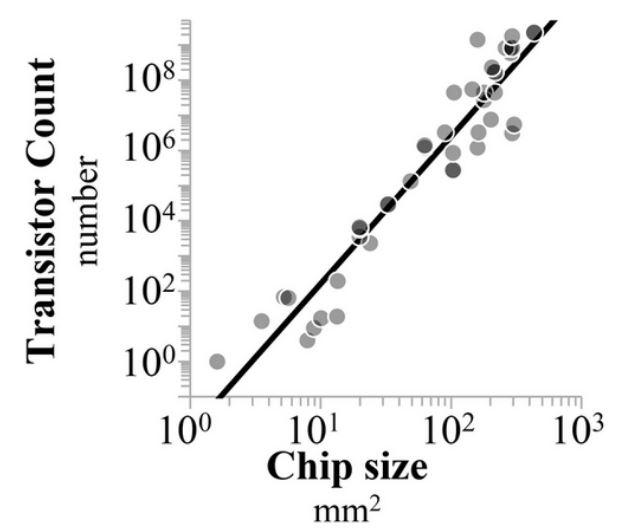

Si l’on considère fixe la taille des puces, ça voudrait dire que l'on double la densité de transistors sur une même surface tous les deux ans. En réalité, pour obtenir ce doublement, on a à la fois une augmentation de la taille de la puce et de sa densité. La densité des transistors est multipliée réellement par 1,75 tous les deux ans en moyenne. Et si faire des grandes puces, ça ne va pas changer grand-chose d'un point de vue des technologies de fabrication, augmenter la densité si !

La taille des puces et leur nombre de transistors. De 1 pour un milimetre carré à 100 milliards pour 10 centimètres carrés. (David Burg, Jesse H. Ausubel)

La densité de transistors sur une surface donnée va dépendre directement de la taille d'un transistor ou d'une cellule unitaire de plusieurs transistors composant une porte logique. De combien on peut fourrer de transistors si on tasse bien, si vous voulez. Il est certain que ça peut dépendre de quel type de puce vous allez faire (une puce logique, une RAM, etc.), mais la tendance est la même.

Densité de transistors dans les puces Intel au fil des années (David Burg, Jesse H. Ausubel)

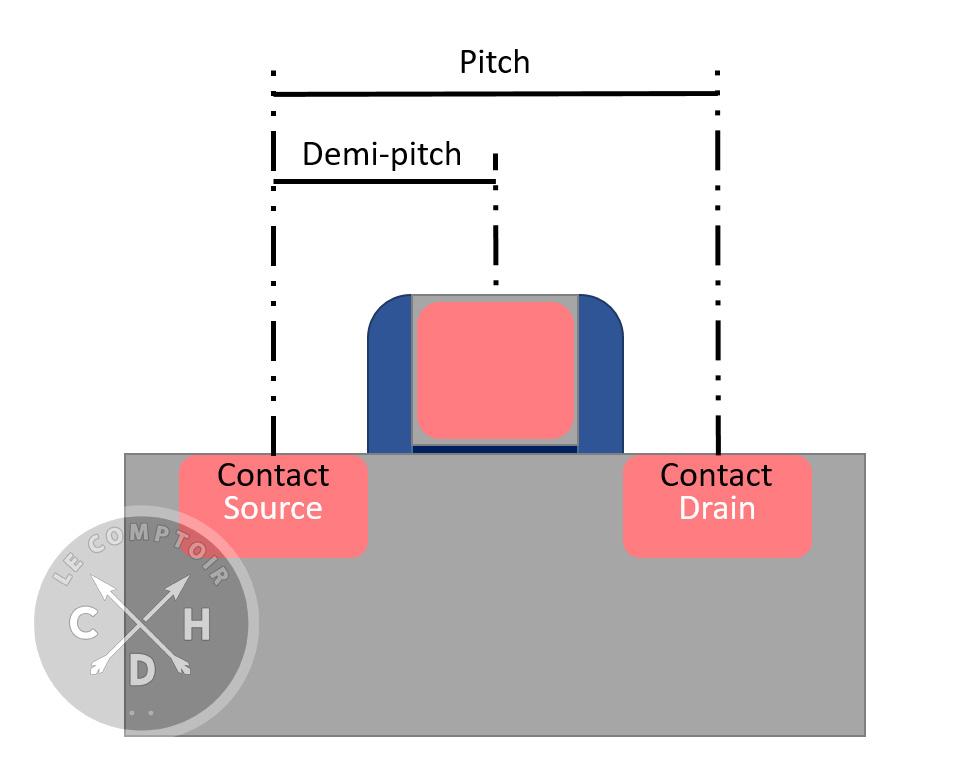

Pour éliminer ces considérations de dessin de circuits, l'industrie s'est d'abord entendue sur une dimension caractéristique du transistor, le demi-pitch, qui fera office de valeur de comparaison. On va donc décrire une intégration de procédés donnée par son demi-pitch minimum, qui sous-entendra sa densité toutes choses égales par ailleurs. Et plus le pitch est petit, mieux ce sera ! C'est la naissance des dénomination des nœud technologiques

Ce demi-pitch sera donc la distance des contacts de la source ou du drain au milieu de la grille. Un transistor du nœud 500 nanomètres fera donc 1 micromètre de la source au drain, un peu plus avec les marges autour du transistor (qui feront aussi 500 nm au mieux).

|

|

| Un poil avant ?La guerre du frame generation | Un peu plus tard ...Test • Gelid Solutions HeatPhase Ultra |  |