Hard du Hard • La Course aux Nanomètres - Partie 2 |

————— 27 Novembre 2023

Hard du Hard • La Course aux Nanomètres - Partie 2 |

————— 27 Novembre 2023

L'intégration Planar est ancienne : le concept n’a pas changé depuis les années 80. Contrairement aux transistors bipolaires qui se construisent autour d’un pilier en silicium (une Mesa), le concept du transistor planar est d’utiliser certaines zones de la surface du wafer comme canal, source et drain, et d’y ajouter la grille au-dessus.

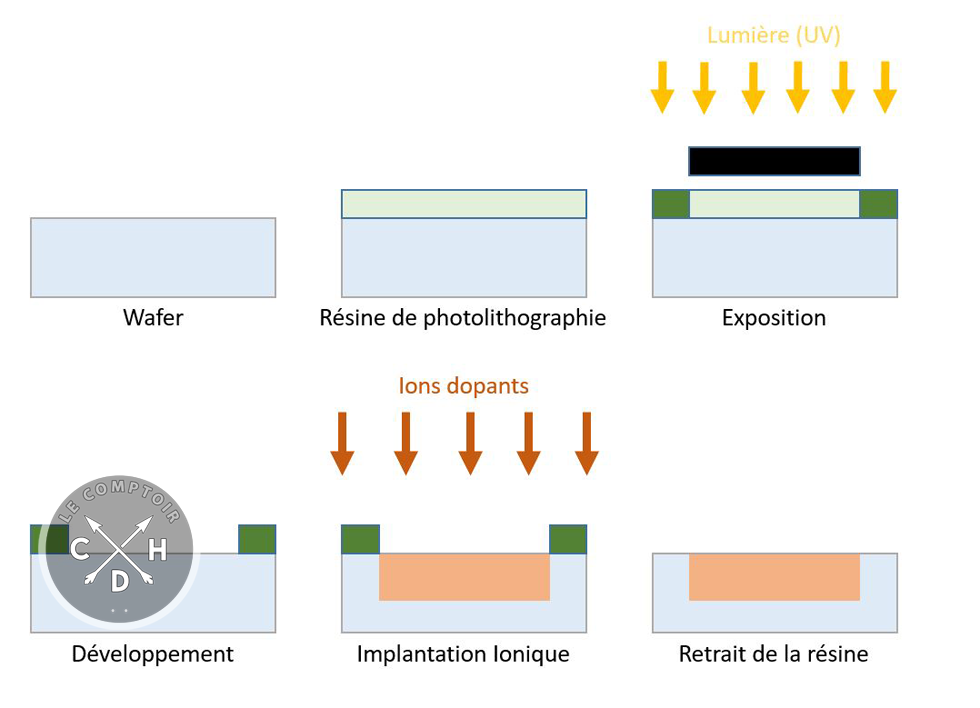

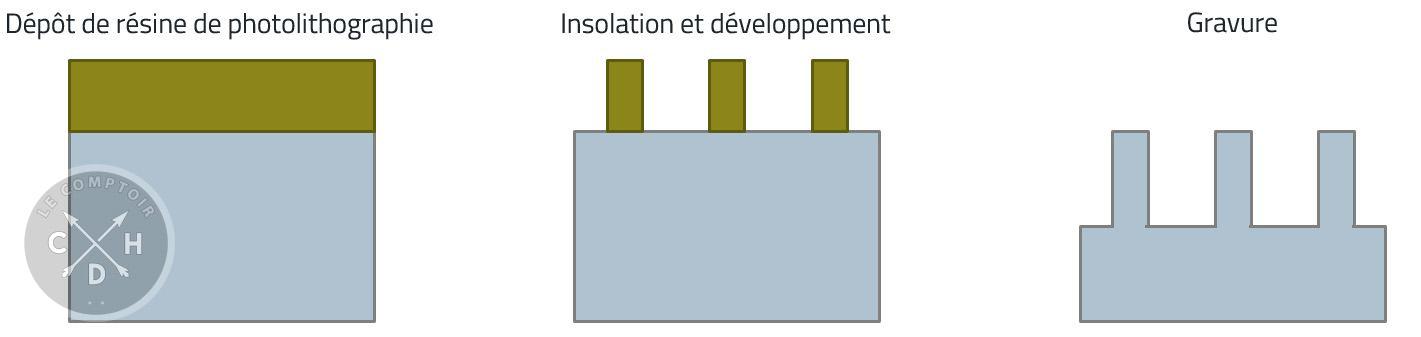

Après les trenches et le well, on va en général commencer par implanter le canal. C’est une implantation en surface du même type de dopants que le well (ou le wafer de base). Il va donc falloir déposer une résine de lithographie partout, l’insoler et la retirer là où on veut implanter. Et recommencer pour l’autre type.

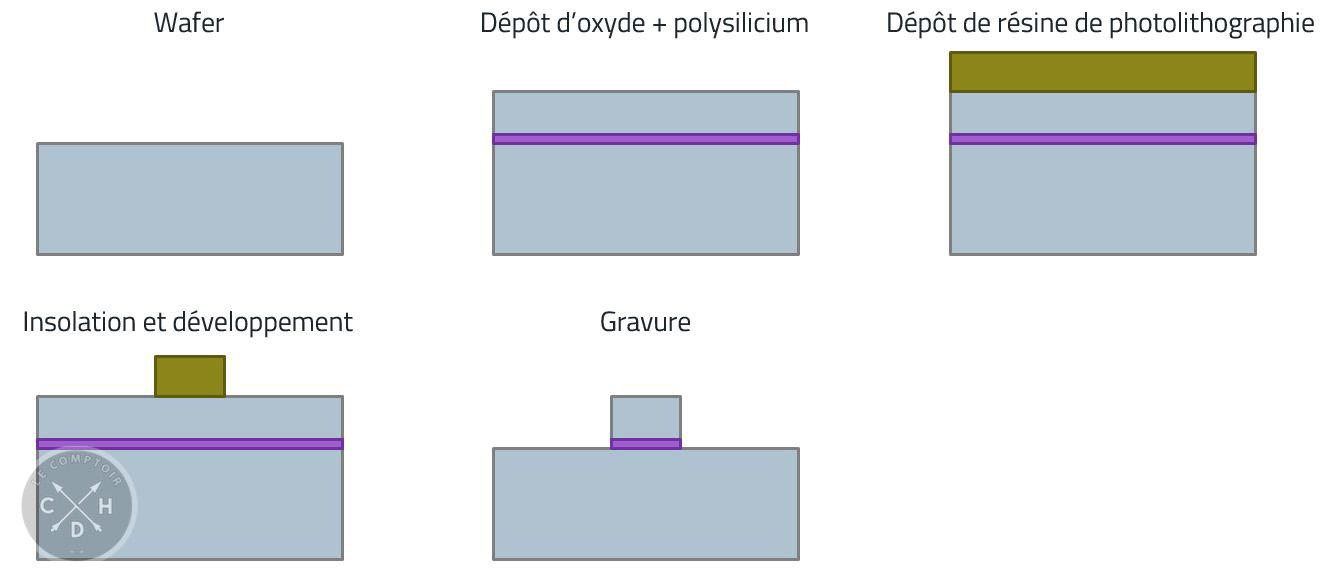

Ensuite, on va déposer un stack de grille. Initialement, on avait un isolant très simple : l’oxyde de silicium. Mais assez vite, il a fallu plus fort. Les électrons de la grille vont créer le champ électrique qui contrôle le flux des électrons dans le canal, il faut donc que ces électrons puissent se déplacer facilement, mais qu’ils ne puissent pas traverser l’oxyde. Au-dessus de cet oxyde, on dépose du silicium. On grave ensuite le silicium et l’oxyde partout, sauf là où on souhaite avoir une grille.

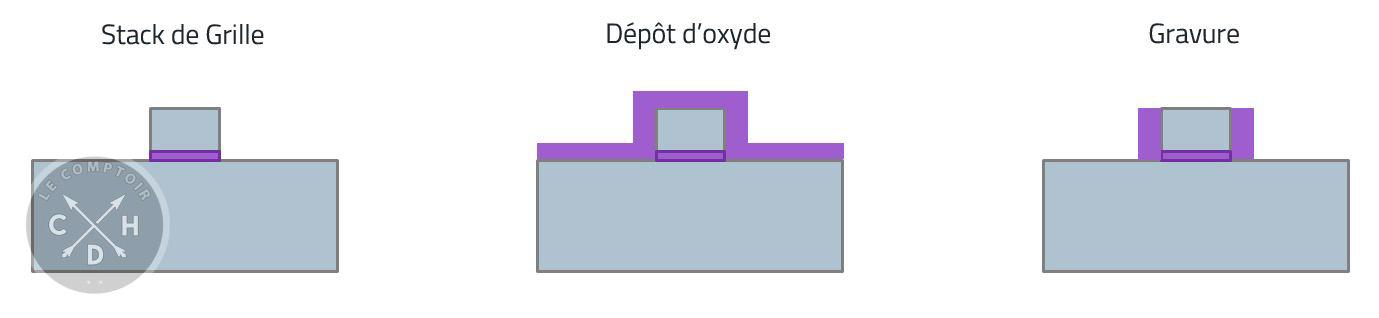

On va créer des espaceurs en déposant un isolant (oxyde de silicium ou nitrure de silicium) très conforme (qui épouse les reliefs créés auparavant), puis en faisant une gravure très directionnelle. Ces espaceurs vont isoler la grille des sources et drain qu’on va créer.

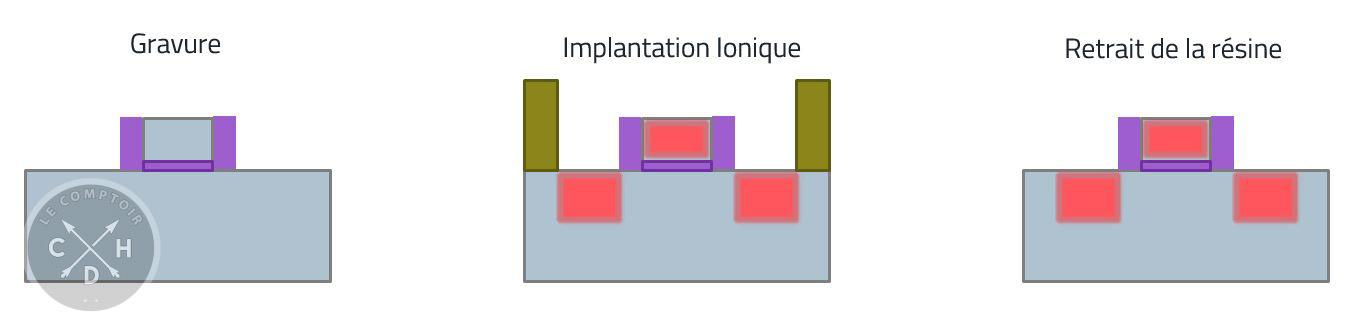

Ensuite, on implante la source et le drain de chaque type (P-MOS et N-MOS). On peut utiliser la grille et les espaceurs comme masque d’alignement pour ne pas s’embêter : on a besoin que la grille soit dopée, et l’isolant des espaceurs n’est pas affecté par le dopage. On appelle ça une technologie auto-alignée.

Le problème majeur du Planar, c’est d’arriver à maintenir un bon contrôle sur le canal quand on voudra le miniaturiser. En effet, en réduisant la taille de la grille par rapport à la tension du transistor, le champ électrique de la grille n’est plus capable d’arrêter les électrons entre la source et le drain. Mais on parlera de ça en détail au prochain article.

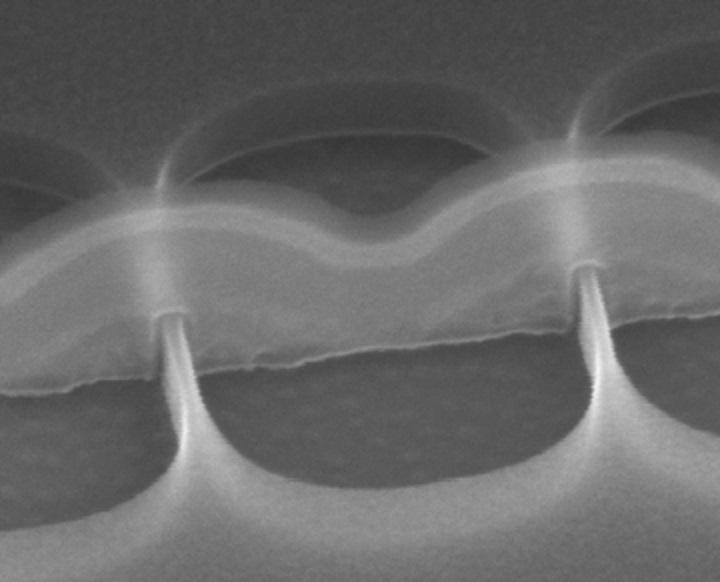

Apparu dans les années 2010, le FinFET est une évolution majeure du Planar. Étant donné qu’il devenait trop difficile de contrôler le passage des électrons, qui avaient trop d’énergie pour être stoppés par l’effet de champ de la grille, on a décidé de doubler la surface de la grille - mais sans agrandir le transistor.

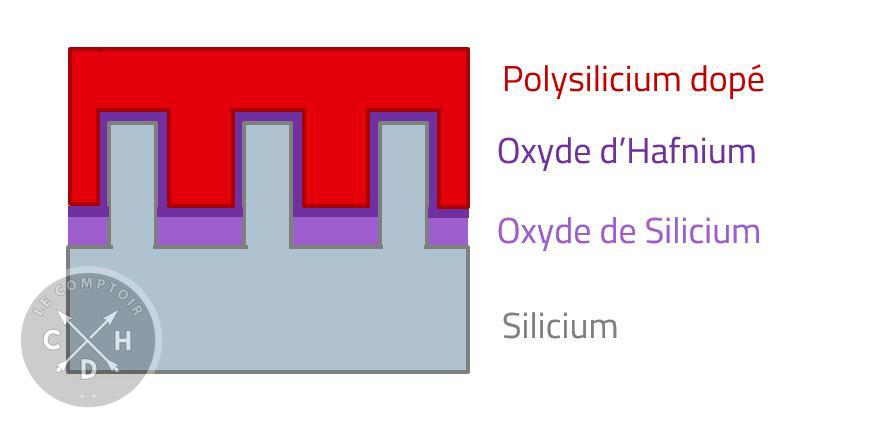

Pour cela, on va surélever la surface du silicium afin de créer un aileron (un Fin, pour FinFET). On va donc faire un dépôt épitaxial de silicium (initialement dopé, mais laissé neutre dans les Fin les plus fins), puis on viendra faire une lithographie dessus, puis une gravure sèche et un stripping. Cette étape, la gravure FinFET est le premier point le plus critique de l’intégration des procédés.

On va faire cette étape une deuxième fois si le silicium déposé pour les Fin est dopé. On va vouloir isoler la Zone Active, qui ne doit être en contact actif que du Fin, ainsi on va déposer un oxyde très directionnel sur toute la plaque. On enlève l’oxyde qui s’est déposé sur le sommet des fins avec un polissage mécano-chimique.

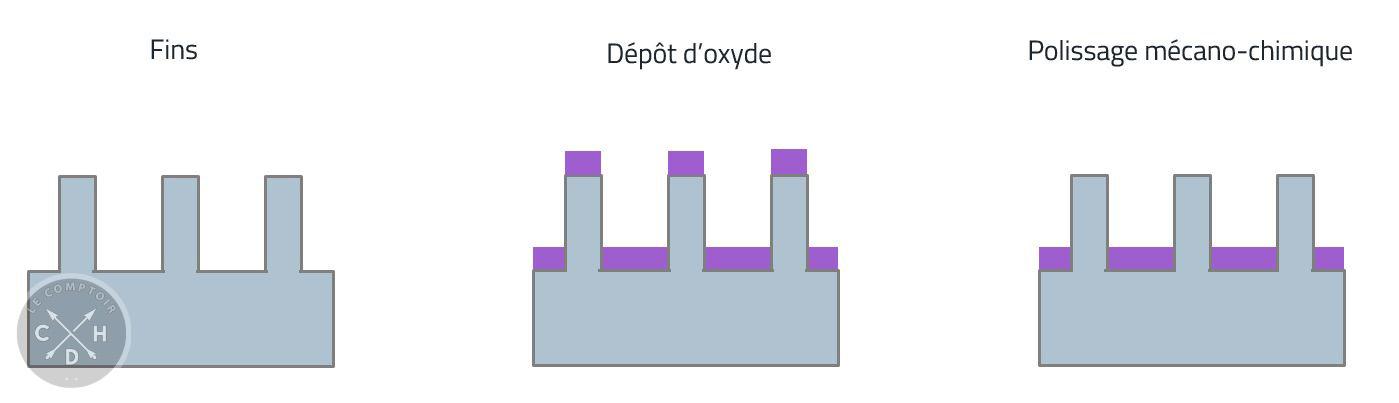

On dépose ensuite l'empilement de grille, comme pour le Planar. Avec un oxyde de grille très isolant (de l’oxyde d’Hafnium, par exemple), puis du silicium polycristallin très dopé (du même type que les contacts), aussi remplacé par un métal dans les puces les plus performantes.

On va aussi vouloir doper la partie du Fin sous les contacts source et drain. Pour cela, on fera comme pour le Well, mais avec des énergies d’implantation très faibles (on veut doper en surface). On pourra avoir déposé un espaceur avant, et utiliser la grille comme masque. On doit faire ça pour les P-MOS, puis les N-MOS.

On fait une photolithographie, on vient graver ce stack de grille pour faire une barrette perpendiculaire au finfet, puis on retire ce qu’il reste de résine de litho. La gravure grille est un peu moins critique que la gravure des Fin.

On a ici la structure globale du FinFET. Certaines intégrations vont différer (on fait la grille avant l’implantation des S/D ou après), parfois on dépose une “fausse grille” qu’on vient remplacer après, mais le principe est toujours le même. Contrairement au Planar, ici la grille entoure l’intégralité du canal : le champ électrique qui empêche les électrons de le traverser est fort, donc on maîtrise mieux cette traversée, même à très petite échelle. Par contre, c’est au prix de procédés bien plus compliqués et critiques.

|

|

| Un poil avant ?Test • NZXT Kraken 240 RGB, Kraken Elite 240, Kraken Elite 360 | Un peu plus tard ...Publicité in game : qui s'y frotte s'y Ubi |  |

| 1 • Préambule |

| 2 • Le CMOS, pourquoi ? |

| 3 • |

| 4 • Le Backend et la Route Technologique |