Hard du Hard • La Course aux Nanomètres - Partie 2 |

————— 27 Novembre 2023

Hard du Hard • La Course aux Nanomètres - Partie 2 |

————— 27 Novembre 2023

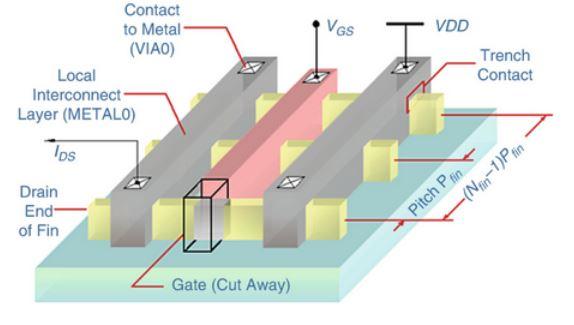

Une fois que l’on a fait nos transistors,on va les noyer dans de l’isolant (un oxyde de silicium, parfois avec une couche de nitrure de silicium), on va ouvrir des trous dans cet isolant au niveau des Well, des Grilles, des sources et des drains, puis on dépose une couche d'accroche en nitrure de titane, que l'on grave à la bonne taille et on remplit de métal (Tungstène ou Cobalt).

Cette brique est même, dans les intégrations les plus récentes, remplacée par le dépôt d'une ligne complète plutôt qu'un plot, qu'on considère comme le niveau Métal 0. La gravure des contacts est la 2e brique la plus critique pour un transistor FinFET, et la plus critique pour un Planar.

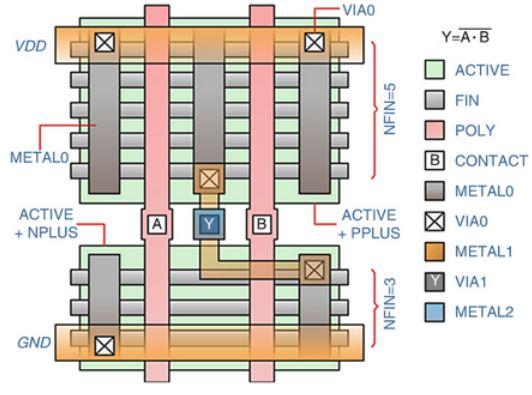

On va créer un Via de niveau 0 en répliquant la même méthode que pour les contacts. À partir du niveau Metal 1, on va se permettre d’utiliser du cuivre plutôt que du Tungstène, car le cuivre conduit beaucoup mieux l’électricité, mais se diffuse très bien dans le silicium, et donc pourrait perturber le fonctionnement du transistor s’il était mis en Metal 0.

Une cellule NAND FinFET complète, dont les entrées sont A et B et la sortie Y.

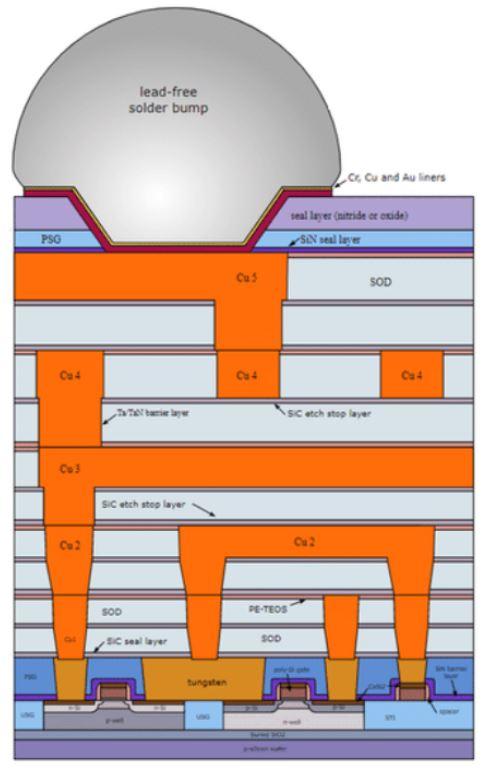

Et après ça ? Et bien on va empiler les Briques Lignes et Vias en technologie damascène pour former un réseau de connexions comme celui-ci. Un niveau de ligne plus un niveau de via formera ce qu’on appelle un niveau de métal.

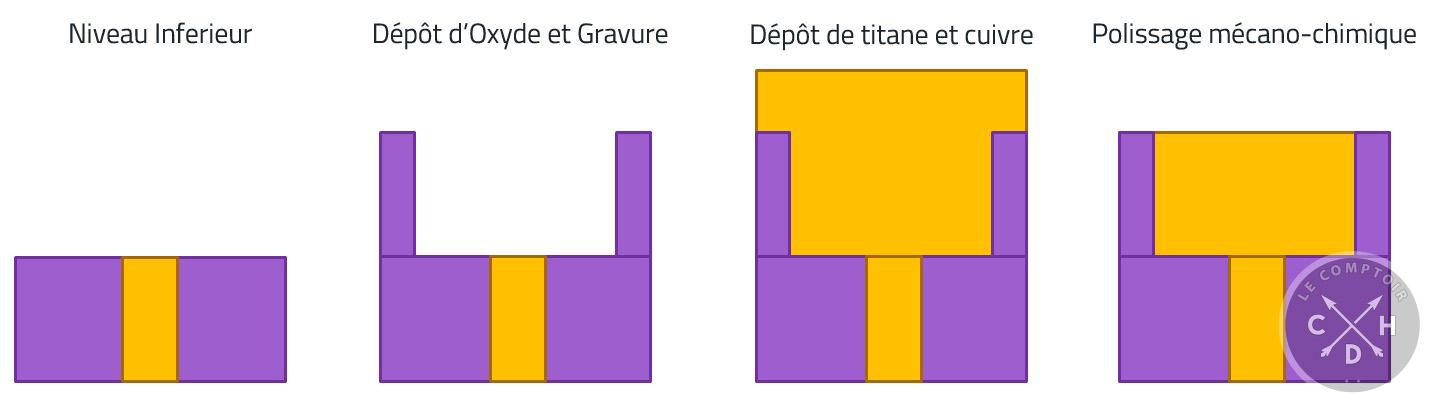

Une brique damascène va être simple : dépôt d'oxyde, litho, puis gravure des lignes, dépôt d'une très fine couche de titane puis de cuivre. Ensuite, on dépose électrochimiquement un gros volume de cuivre. Une CMP viendra aplanir le tout au niveau de l'oxyde. Une puce moderne est tellement dense qu’elle peut nécessiter jusqu’à 15 niveaux de métal.

Lorsqu’un fondeur a mis au point l’enchaînement des briques qui lui permet de faire une puce fonctionnelle, on dit que c’est une Route Technologique. Cette route va définir quels composants (P-MOS, N-MOS, résistances, capacités) vont pouvoir être fabriqués, à quelle taille, à quel écartement, et quels masques de lithographies doivent être conçus. Les concepteurs de puces vont s’emparer de ces règles de dessin et vont créer les plans de la puce. Ces puces seront réalisées en répétant les étapes de la route technologique, avec comme spécificité d’utiliser les masques de lithographie que les dessinateurs auront conçus. Une route technologique permet donc de fabriquer de nombreuses puces, tant qu’elles respectent les règles de dessin.

Miniaturiser les transistors implique donc de faire en sorte que tout le procédé, du Well au dernier Métal, soit compatible avec des dimensions de photolithographie, de gravure, de dopage plus petites, et que le transistor marche quand même à la fin. Et c’est important de miniaturiser : on le verra au prochain article.

|

|

| Un poil avant ?Test • NZXT Kraken 240 RGB, Kraken Elite 240, Kraken Elite 360 | Un peu plus tard ...Publicité in game : qui s'y frotte s'y Ubi |  |

| 1 • Préambule |

| 2 • Le CMOS, pourquoi ? |

| 3 • Le Planar et le FinFET |

| 4 • |