Hard du Hard • La Course aux Nanomètres - Partie 2 |

————— 27 Novembre 2023

Hard du Hard • La Course aux Nanomètres - Partie 2 |

————— 27 Novembre 2023

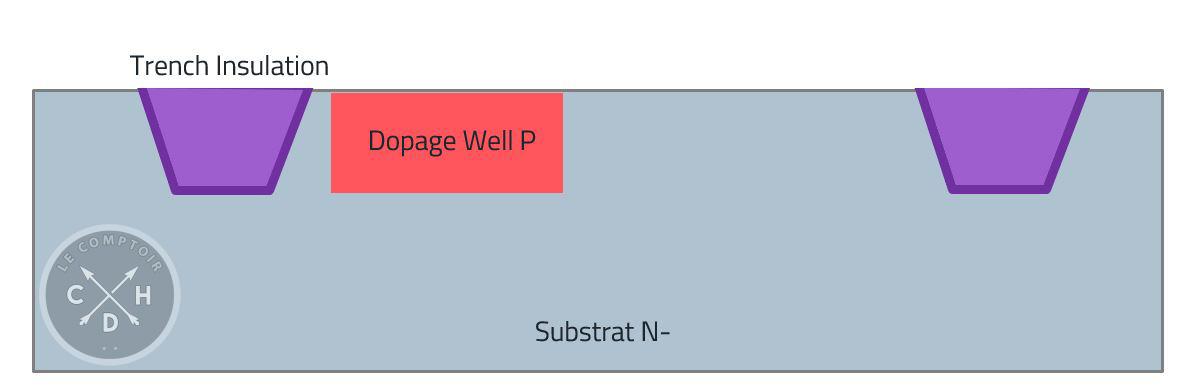

Reprenons : la dernière fois, nous avons dopé notre wafer de silicium dans la brique Well ou Zone Active, puis nous avons séparé les différents transistors et dispositifs avec les Shallow Trench Insulation et les Deep Trench Insulation. Nous avons la fondation de notre transistor à effet de champ CMOS (Complementary Metal-Oxyde-Semiconductor Field Effect Transistor).

La dernière fois, on avait fabriqué ça

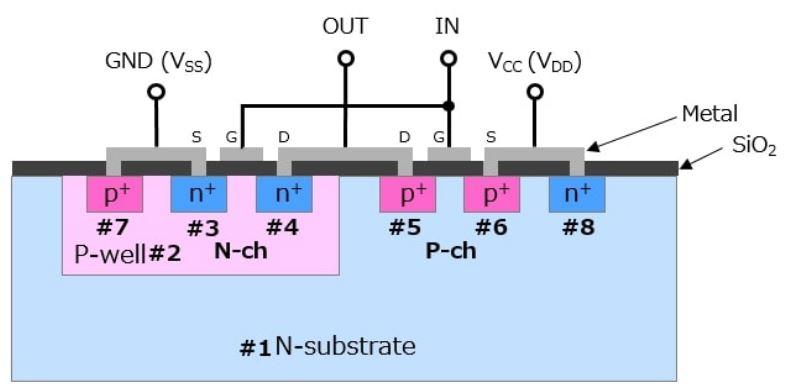

Le CMOS consiste en des transistors, ou des cellules de plusieurs transistors à effet de champ. Un transistor à effet de champ va, dans le principe, contrôler le passage du courant entre la source et le drain par une tension appliquée sur sa grille (qui créera un champ électrique dans le canal, entre la source et le drain). Certains sont des transistors N et d’autres des transistors P, leur désignation venant du dopage des source et drain. La combinaison de ceux-ci permettent de créer des portes logiques qui donneront des résultats différents. Ensuite, toutes ces portes logiques seront reliées les unes aux autres pour former des unités de calcul, des cellules mémoire, etc.

Un inverseur CMOS. OUT sera nul si IN dépasse le seuil d’activation des transistors.

Toutes les portes logiques peuvent être créées sur ce principe, en assemblant plusieurs transistors P avec plusieurs transistors N. Le très gros avantage du CMOS est sa faible consommation de courant. En effet, si on voulait faire une logique avec seulement des N-MOS ou des P-MOS, il y aurait une dissipation de courant permanente et un risque que la tension en sortie de l’inverseur soit trop faible pour activer/désactiver les transistors qui suivent. Le CMOS utilise donc les P-MOS comme pull-up et les N-MOS comme pull-down, permettant à la porte logique de sortir des 1 et des 0 les plus nets possibles (et donc de pouvoir en mettre plein à la suite) avec une dissipation de chaleur (relativement) faible.

Une fois que l’on a fait le choix du CMOS et réalisé nos DTI, STI et Well, il va falloir réaliser le canal à électrons, le cœur du transistor. Et pour cela, il y a actuellement deux méthodes sur le marché : la technologie Planar et la technologie FinFET.

|

|

| Un poil avant ?Test • NZXT Kraken 240 RGB, Kraken Elite 240, Kraken Elite 360 | Un peu plus tard ...Publicité in game : qui s'y frotte s'y Ubi |  |

| 1 • Préambule |

| 2 • |

| 3 • Le Planar et le FinFET |

| 4 • Le Backend et la Route Technologique |