Hard du Hard • La Course aux Nanomètres - Partie 1 |

————— 02 Novembre 2023

Hard du Hard • La Course aux Nanomètres - Partie 1 |

————— 02 Novembre 2023

Mais le Procédé, ce n'est que le début. L'objectif c'est de faire des puces. Donc on va vouloir faire des transistors, puis les relier entre eux par des lignes de cuivre. Les transistors vont être la partie front-end de la puce, les interconnexions métalliques de la partie back-end. On va partir du bas et construire l'empilement vers le haut en enchaînant les procédés.

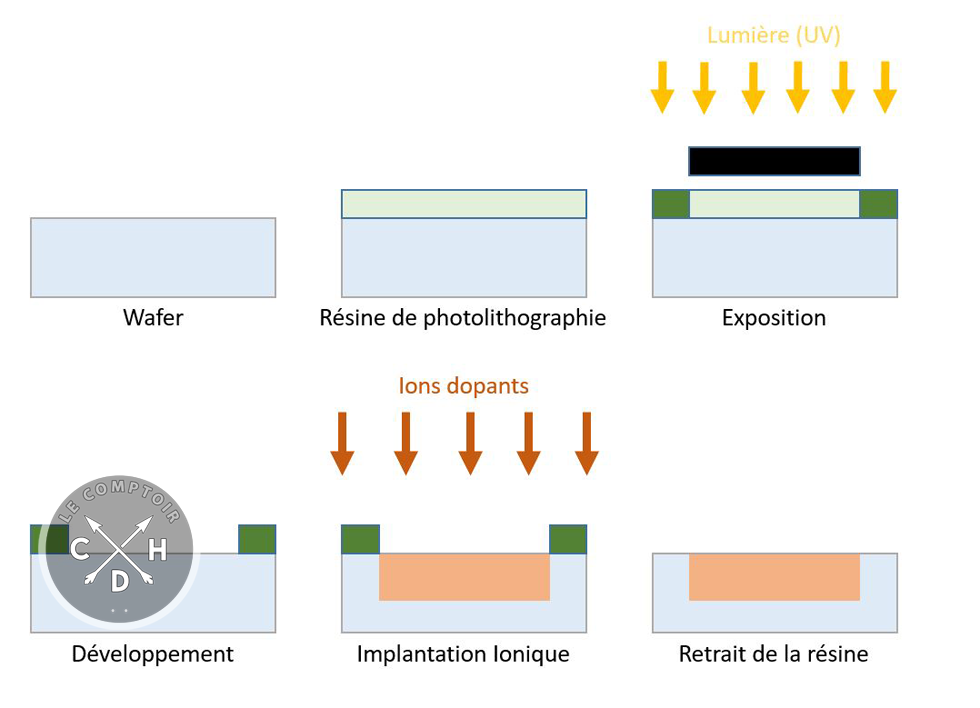

Par exemple, pour produire une puce CMOS, on va commencer par vouloir doper le silicium, c'est-à-dire lui injecter des atomes qui modifieront les propriétés électriques du silicium uniquement à certains endroits — on verra pourquoi et comment plus tard.

On va d'abord couvrir de résine de photolithographie les zones que l'on veut maintenir non-dopées. Puis on va implanter des dopants, des atomes de bore, d'arsenic ou de phosphore. Puis on va retirer la résine dans une étape de stripping. On viendra finalement — après le retrait de la résine qui sinon brûlerait — recuire le wafer quelques secondes à température supérieure à 1000 °C pour activer les dopants, c'est-à-dire les faire rejoindre leurs sites atomiques dans le cristal de silicium. On va appeler cette séquence de procédés une Brique, ou B.

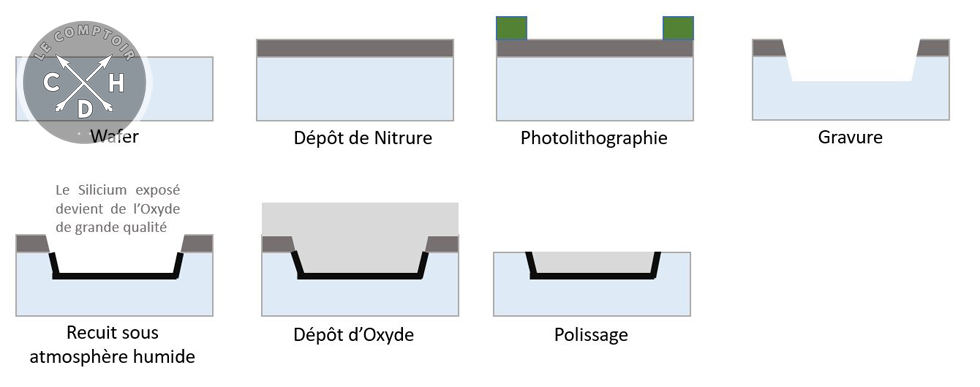

Après cela on séparera les différents composants de la puce par de grosses tranchées ou des petites tranchées, en fonction de ce qu'on veut isoler électriquement. Pour faire ces tranchées, on va d'abord couvrir de résine de photolithographie les zones que l'on ne veut pas creuser, on va graver le silicium, retirer ce qu’il restera de résine de photolithographie puis on déposera de l'isolant, en une ou deux fois. Et on enlèvera le surplus de dépôt par un polissage mécano-chimique. Ces briques DTI (Deep Trench Insulation) et STI (Shallow Trench Insulation) qui auraient du être à priori "simples", vont donc se décomposer en 7 P différents, avec plusieurs S chacun.

Ces deux exemples de Briques sont les « fondations » du transistor, qui existent dans toutes les puces de logique CMOS sur le marché. Si les Procédés étaient des étapes conceptuelles de travail sur des couches minces, la Brique sera donc en général la fabrication d’un élément identifiable de transistor — ici, les trench insulations et la zone active — à partir d’une somme de procédés. Plus haut dans la puce, quand on va vouloir relier plusieurs transistors entre eux, on parlera d’une brique « Lignes » pour faire… Un des niveaux de fils de cuivre entouré d’isolants.

![3N C11QU4N7 C357 P1U5 6r4ND interco cuivre [cliquer pour agrandir]](/images/stories/articles/hdh/process-nodes/interco_cuivre_t.jpg) Photo des premières interconnexions en cuivre d’IBM (sans l’isolant autour) en 1997. Chaque niveau est une brique.

Photo des premières interconnexions en cuivre d’IBM (sans l’isolant autour) en 1997. Chaque niveau est une brique.

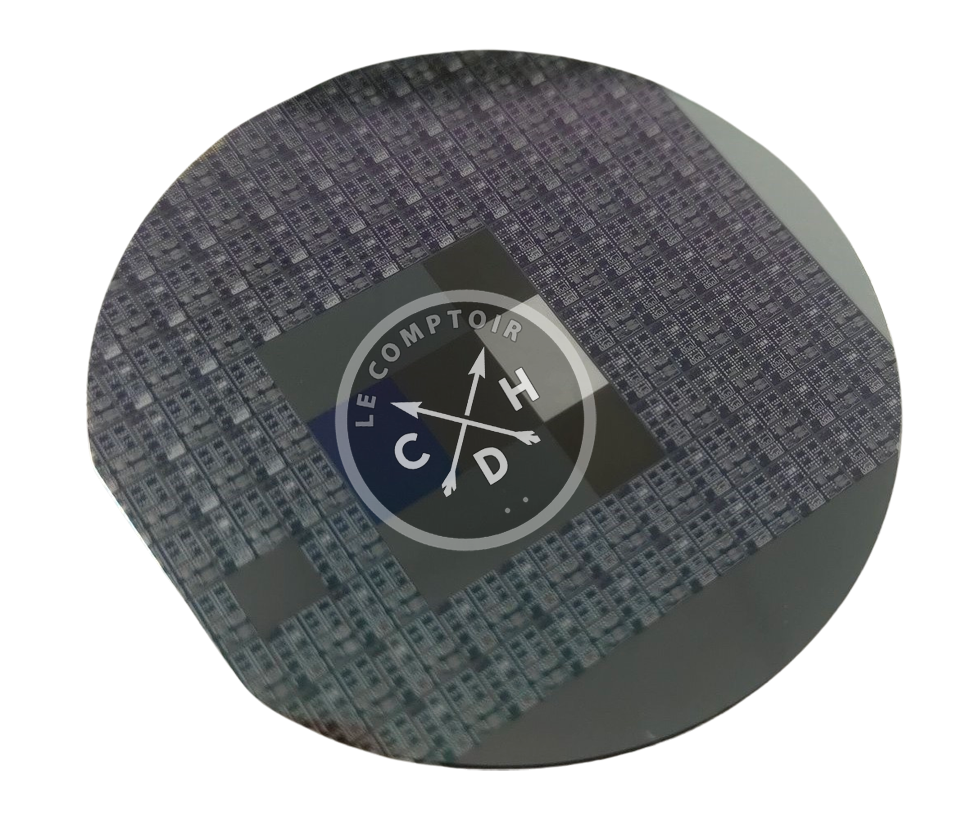

Et puisque nous travaillons dans des intégrations de très, très, trèèèèèès nombreux transistors, si l’on produit un élément de transistor comme un DTI ou une zone active, on peut en produire des milliards sur un seul wafer ! Il suffit que le masque de photolithographie ait ces milliards d'éléments.

Là il n’y a que quelques dizaines de transistors, mais au moins vous n’avez pas besoin de microscope électronique pour les voir.

Là il n’y a que quelques dizaines de transistors, mais au moins vous n’avez pas besoin de microscope électronique pour les voir.

Pour faire un transistor, il va falloir de nombreuses briques qu'on verra ensemble au prochain article, mais une brique peut aussi correspondre à d'autres composants. Par exemple, TSMC a mis dans certaines de ses technologies CMOS une possibilité d’intégrer de la mémoire RAM non-volatile magnétique. Cette cellule MRAM est une brique ajoutée à l'enchaînement "classique" de la fabrication des puces. Cet ajout va permettre aux concepteurs de circuit d’avoir les fameuses cellules de MRAM disponibles dans leurs designs, et quelques étapes en plus en fabrication pour le fondeur.

Au prochain article, nous verrons comment ces Briques s'enchaînent pour fabriquer les transistors, leurs interconnexions et enfin les puces elles-mêmes. Cela nous permettra de clarifier ce qu’est une route technologique.

|

|

| Un poil avant ?En cabine • Corsair HS80 Max Wireless | Un peu plus tard ...Test • NZXT H6 Flow RGB |  |