La DDR5 semble avoir un potentiel d'overclocking intéressant |

————— 08 Octobre 2021 à 17h38 —— 21356 vues

La DDR5 semble avoir un potentiel d'overclocking intéressant |

————— 08 Octobre 2021 à 17h38 —— 21356 vues

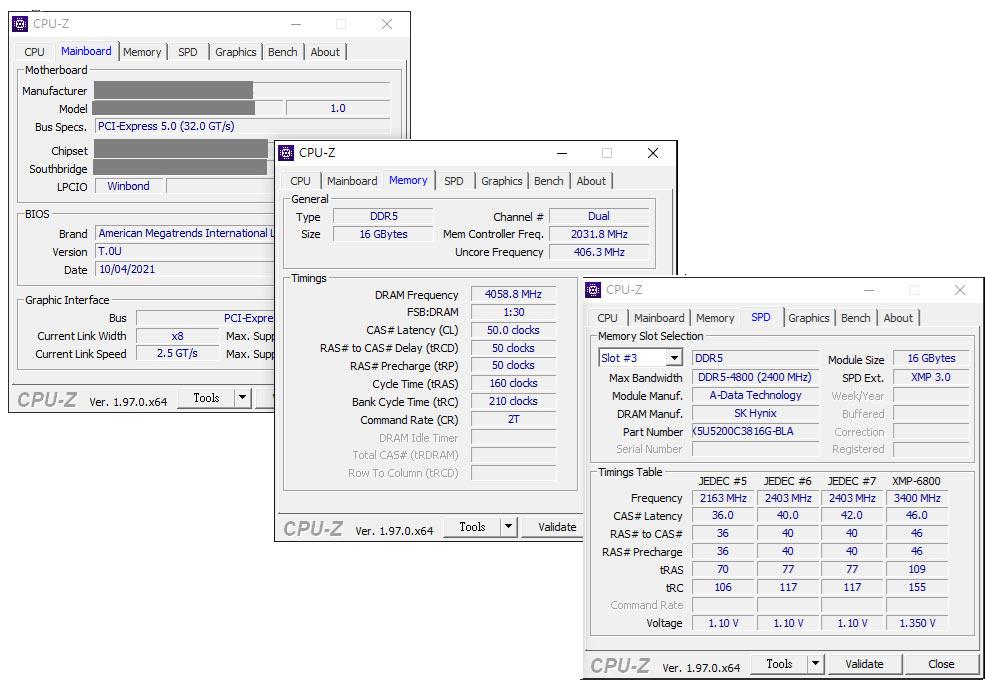

La DDR5 va commencer à arriver un peu partout, et si tous devraient proposer des kits de DDR5 4800 qui constituent le standard JEDEC, ils devraient avoir un catalogue plus fourni en références. Hier, c'était Colorful qui teasait sa DDR5 6333, on sait que chacun ira de sa création pour attirer le client. ADATA a publié quelques screens CPU-Z, qui permettent de voir le potentiel de ses barrettes. La capture montre qu'il y a deux barrettes utilisées, de 16 Go chacune. Les profils enregistrés sont typiques du JEDEC, à savoir DDR5 4333 CAS 36, 4800 CAS 40 et 42, mais aussi un spécifique au kit. Ce sont des DDR5 6800 CAS 46-46-46-109-155 à 1,35 V.

Mais la dernière capture montre une fréquence de 4058,8 MHz, ce qui donnerait de la DDR5 8118, au prix bien entendu de latences bien relâchées. On passe sur du cas 50-50-50-160-210 pour arriver à une telle fréquence, mais cette montée en puissance reste intéressante, surtout quand on songe que c'est la première génération, le cas échéant des puces SK Hynix. La grande question, vu que la technologie est nouvelle, c'est de savoir comment les processeurs Alder Lake, les premiers à s'en servir sur le marché, sauront tirer parti de cette fréquence haute, mais contrebalancée par ces latences plus lâches que le sphincter de Nicolas.

| Un poil avant ?La bêta de Battlefield 2042 en test GPU | Un peu plus tard ...Back 4 Blood vient silencieusement d'ajouter... le DRM Denuvo |  |