Après Rocket Lake, au tour d'Alder Lake de fuiter sur GeekBench |

————— 29 Décembre 2020 à 17h52 —— 12248 vues

Après Rocket Lake, au tour d'Alder Lake de fuiter sur GeekBench |

————— 29 Décembre 2020 à 17h52 —— 12248 vues

Après des (un peu trop ?) appétissants benchmarks de Rocket Lake, la microarchitecture prévue pour janvier chez les bleus, voici que sa suite a aussi fuité également également via GeekBench. Si la suite de la suite peut sembler un futur plutôt incertain, son nom, Alder Lake, n’est pas vraiment nouveau sur le comptoir, Intel ayant déjà communiqué à ce sujet afin d’occuper l’espace médiatique précédant les fêtes : ces prochains processeurs seront basés sur une topologie hétérogène, c’est-à-dire que les cœurs rassemblés sous l’IHS auront des organisations logiques différentes — et pas seulement des fréquences différentes, comme effectué actuellement.

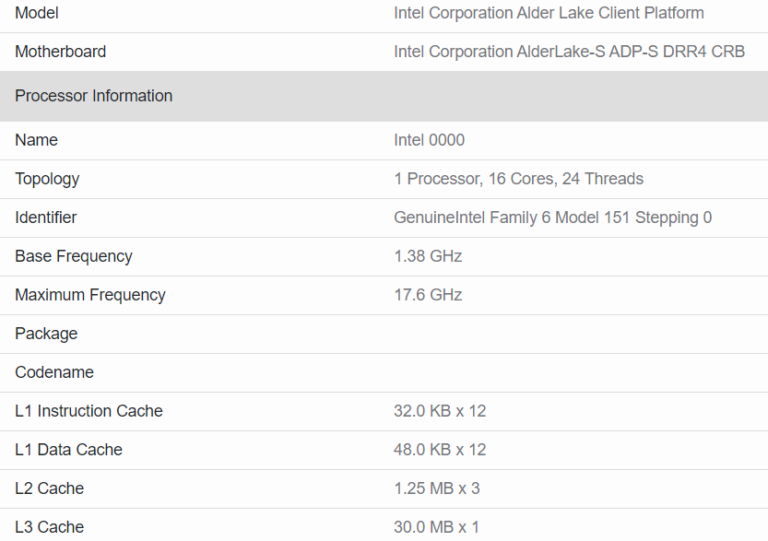

De ce fait, les spécifications fuitées diffèrent de ce à quoi nous avons été habitués sur le segment : pas moins de 16 cœurs physiques (8 gros pour 8 petits), mais, surtout, 24 cœurs logiques, car seuls les plus puissants bénéficieraient de l’hyperthreading... un vrai casse-tête ! Pas étonnant que la détection automatique soit dans les choux : les 1,38 GHz de base semblent être la fréquence des cœurs les plus efficients, et les 17,6 GHz maximum... pas grand-chose de significatif. Au niveau des caches, rien de bien nouveau ; 32 kio de L1-I, 48 kio de L1-D (héritage d’Ice Lake), un L2 de 1,25 Mio par cœur, et un L3 unifié de 30 Mio. Reste à voir comment tout cela se partitionne entre les 16 cœurs ! Pour ce qui est des performances, le score n’est clairement pas bon : 996 points en monocoeur et 6 931 points en multicœurs, c’est presque deux fois moins que le Rocket Lake de ce matin... Ce qui n’est pas si étonnant étant donné le caractère encore très embryonnaire de la production de ce processeur. Un peu plus de Mme Irma, et il est probable que ce bouzin tournait plutôt à 1,76 GHz maximum et soit destiné à une vérification du processus initial de fabrication, et non une optimisation de l’architecture pour des fréquences hautes. Prenez votre mal en patience, les annonces ne devraient pas défiler de sitôt... (Source : VideoCardz)