Le successeur du FinFET se précise de plus en plus : le GAA FET |

————— 24 Février 2020 à 14h12 —— 16224 vues

Le successeur du FinFET se précise de plus en plus : le GAA FET |

————— 24 Février 2020 à 14h12 —— 16224 vues

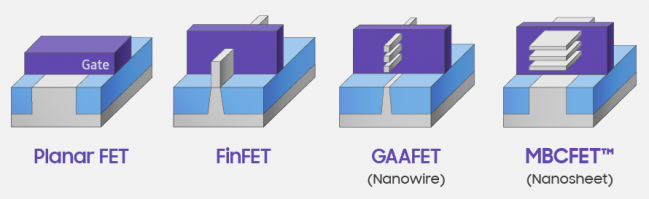

L'amélioration de la finesse de gravure des circuits imprimés et des composants pour la création des puces permet de booster l'efficacité de nos composants informatiques, mais amène à de nouveaux défis. En effet, nous avions vu il y a peu de temps qu'il est difficile de maintenir les mêmes méthodes de conception en dessous des 7 nm, car le traditionnel FinFET ne peut être avantageux à partir de ce seuil. La raison est simple, puisque le FinFET se base sur une structure verticale, il est difficile de trop rapprocher les canaux des transistors entre-eux sous peine d'avoir un effet capacitif entre chaque. La solution est donc de passer des structures à canaux verticaux aux structures à canaux horizontaux, appelées GAA FET et divisées actuellement en deux technologies - dont les méthodes de conceptions sont similaires - appelées Nanowire et Nanosheet.

Il faut savoir avant toute chose que les GAA FET ne sont pas nouveaux, mais leur complexité de fabrication avait laissé la place aux FinFET durant les années 2000. Mais les limitations de cette technologie ont poussé les fabricants à développer les GAA FET depuis quelques années, dans l'objectif de sortir des puces basées sur ce type de transistors dès l'année prochaine. Le procédé de fabrication diffère de peu celui du FinFET : plutôt que de réaliser un mur pour la jonction source/drain, un premier matériau est utilisé pour mettre en forme les feuilles, puis est dissous pour ne laisser que ces feuilles. Par la suite, la grille - gate en anglais - est déposée et chargée.

Les avantages de ces transistors sont la possibilité de proposer pour un seul élément plusieurs canaux - jusqu'à 6 chez TSMC - ce qui permet la réalisation de transistors plus stables et précis. L'avantage est que cette technologie permet de continuer l'amélioration de la finesse de gravure tout en consommant toujours moins que son prédécesseur. Bien entendu, comme la technologie en est à ses débuts sur le plan industriel, il faudra s'attendre à de nombreuses itérations et des différences notables entre les fondeurs. Il ne reste donc plus qu'à attendre les premières puces industrielles basées sur cette technologie, qui sortiront probablement en 2021 ou 2022 en 5nm. (source : Semi Engineering)

| Un poil avant ?Le retour des rumeurs Ampere ! | Un peu plus tard ...Live Twitch • The Last of Us Remastered (Grounded) |  |