Le JEDEC a finalisé la HBM4 : jusqu'à 64 Go et 2 To/s |

————— 19 Avril 2025 à 08h00 —— 16287 vues

Le JEDEC a finalisé la HBM4 : jusqu'à 64 Go et 2 To/s |

————— 19 Avril 2025 à 08h00 —— 16287 vues

Le JEDEC a publié la spécification officielle de la norme HBM4 (High Bandwidth Memory 4), estampillée JESD270-4, le 17 avril. Rien de très original, l'organisme indique que cette norme a été conçue pour répondre aux exigences croissantes des charges de travail en intelligence artificielle (IA) et en calcul haute performance (HPC). Elle apporte diverses améliorations pour accroître la bande passante, la capacité et l'efficacité de la mémoire.

Image d'illustration utilisée par SK Hynix pour annoncer ses premiers échantillons de HBM4 12Hi (19 mars 2025)

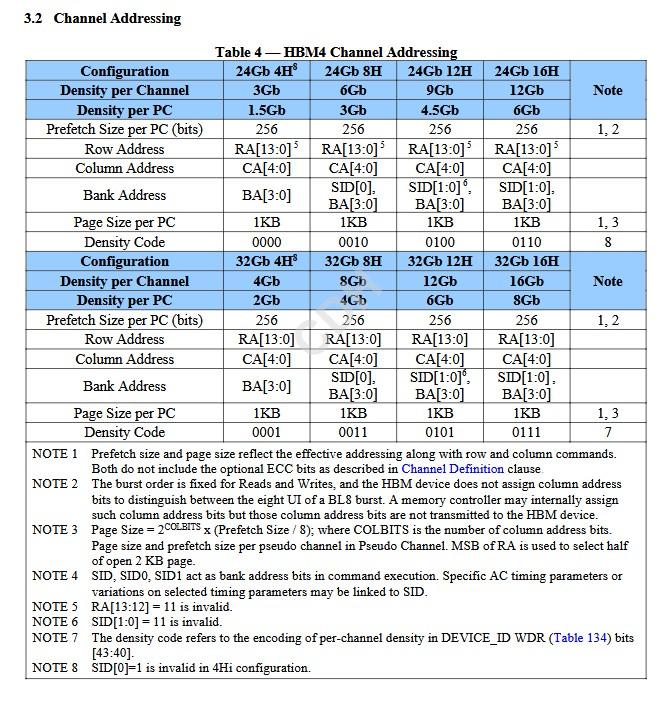

À l’instar des précédentes versions de HBM, la HBM4 repose sur des puces DRAM empilées verticalement. En termes de capacité, HBM4 supporte des configurations de piles de 4 à 16 hauteurs et propose des densités de DRAM allant de 24 Gb à 32 Gb. Cela permet d'atteindre des capacités maximales de 64 Go en utilisant des piles de 32 Gb à 16 étages — c'est 48 Go pour la HBM3E 16-Hi de SK Hynix.

L'une des principales améliorations de HBM4 réside dans le doublement du nombre de canaux indépendants par pile : il passe de 16 à 32, et ajoute des pseudo-canaux. Cette évolution augmente la flexibilité d'accès et le parallélisme dans les opérations mémoire. De plus, la HBM4 sépare les bus de commande et de données, ce qui réduit la latence et améliore la simultanéité des opérations. La norme permet des vitesses de transfert allant jusqu'à 8 Gb/s sur une interface de 2048 bits. La bande passante totale peut atteindre 2 To/s.

D'autre part, la prise en charge de plusieurs niveaux de tension spécifiques, incluant des options comme 0,7V, 0,75V, 0,8V ou 0,9V pour le VDDQ, ainsi que 1,0V ou 1,05V pour le VDDC, contribuent à améliorer l’efficacité énergétique. La HBM4 introduit également le Directed Refresh Management (DRFM). Cette fonctionnalité atténue le row-hammer tout en supportant des fonctions de fiabilité, de disponibilité et de maintenance (RAS — Reliability, Availability, and Serviceability) avancées.

Enfin, la HBM4 reste compatible avec les contrôleurs HBM3 existants. Un contrôleur peut fonctionner à la fois avec de la HBM3 et de la HBM4 si nécessaire. Le JEDEC vante en la flexibilité d’intégration qui en résulte.

Comme en en attestent les nombreuses déclarations du communiqué de presse, la norme HBM4 est le fruit d’une collaboration de plusieurs entreprises, dont Samsung, Micron et SK hynix. Certaines prévoient de lancer la production de HBM4 dans le courant de l’année. Vous trouverez le PDF de 280 pages qui détaille la norme sur le site du JEDEC. L'accès au document est gratuit, il suffit de s'enregistrer.

| Un poil avant ?NVIDIA dégaine les pilotes 576.02, la fin des galères pour les RTX ? | Un peu plus tard ...Les Nova Lake-S mettraient les cartes mères LGA-1851 à la retraite |  |

128Go à 4To/sec ca pourrait envoyer du pate dans un form factor sympa. Je ne comprends pas pourquoi ca n'est pas utlisé pour le grand public, c'est si cher à produire ? On voit bien des carte graphique à 3000€ qui se vendent à la pelle, pourquoi pas un laptop à 3000€.

Lors des annonces de l'HBM 2 et 3 les prix étaient encore bien hauts.