TSMC prépare CoPoS : du wafer rond au panneau rectangulaire |

————— 12 Juin 2025 à 16h57 —— 28757 vues

TSMC prépare CoPoS : du wafer rond au panneau rectangulaire |

————— 12 Juin 2025 à 16h57 —— 28757 vues

Chez TSMC, la technologie CoWoS (Chip-on-Wafer-on-Substrate) est en place depuis plusieurs années. Mais contrairement à ce que vous faites méthodiquement tous les soirs dans votre cuisine, à savoir réutiliser les chutes de vos préparations soigneusement taillées à l’emporte-pièce, c'est plus compliqué de rentabiliser les wafers circulaires lorsque l’on y prélève des modules rectangulaires : cette contrainte géométrique entrave l’optimisation.

Pour y remédier, TSMC prévoit de changer d’approche, en passant du wafer rond au panneau rectangulaire. Selon MoneyDJ et Economic Daily News (via TrendForce), le fondeur taïwanais lancera dès 2026 une ligne pilote dédiée à la technologie CoPoS (Chip-on-Panel-on-Substrate), avec une montée en production de masse prévue pour 2029.

Le Wafer Scale Engine de Cerebras (monolithique)

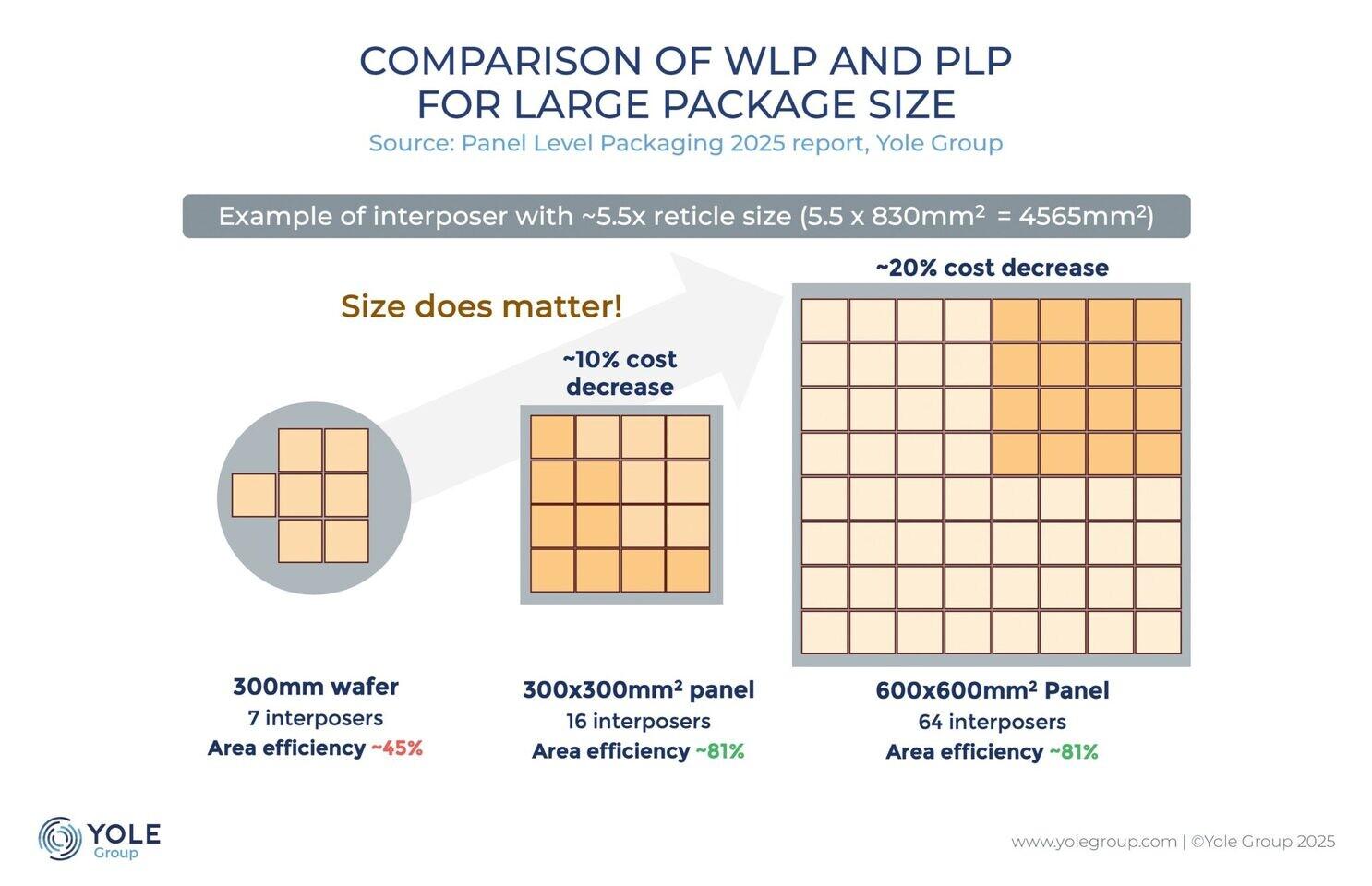

Là où CoWoS se limite à des substrats découpés de 120 × 150 mm, CoPoS ambitionne de porter cette surface à 310 × 310 mm dès le départ. Et d’après un papier du Yole Group paru en mars, les formats pourraient grimper jusqu’à 600 × 600 mm dans les futures solutions PLP (Panel-Level Packaging) — image ci-dessous. Forcément, le passage du WLP (Wafer-Level Packaging) au PLP promet une réduction notable des coûts de production, tout en offrant plus de surface exploitable pour intégrer mémoire HBM, chiplets I/O et dies de calcul dans un même packaging.

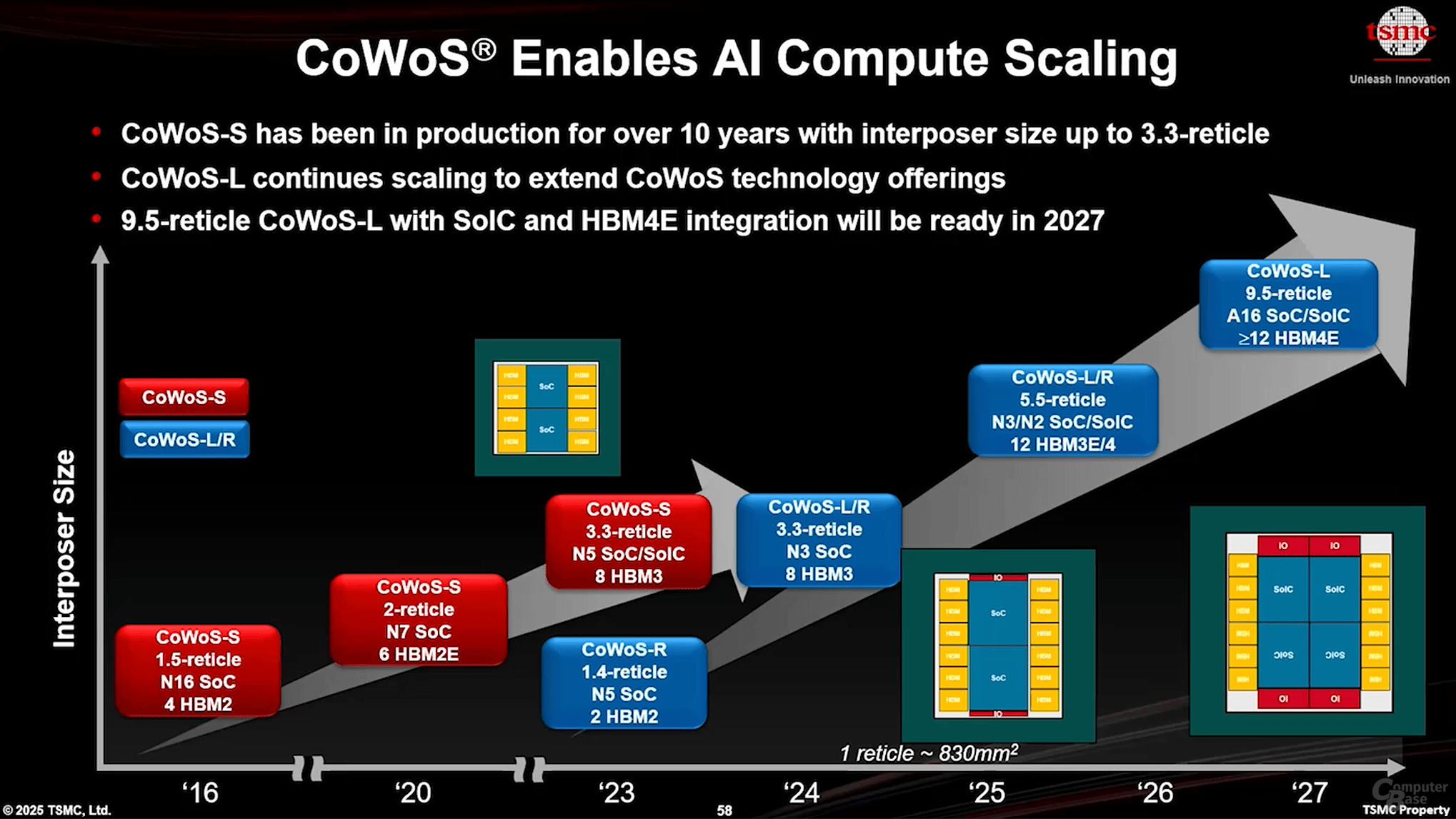

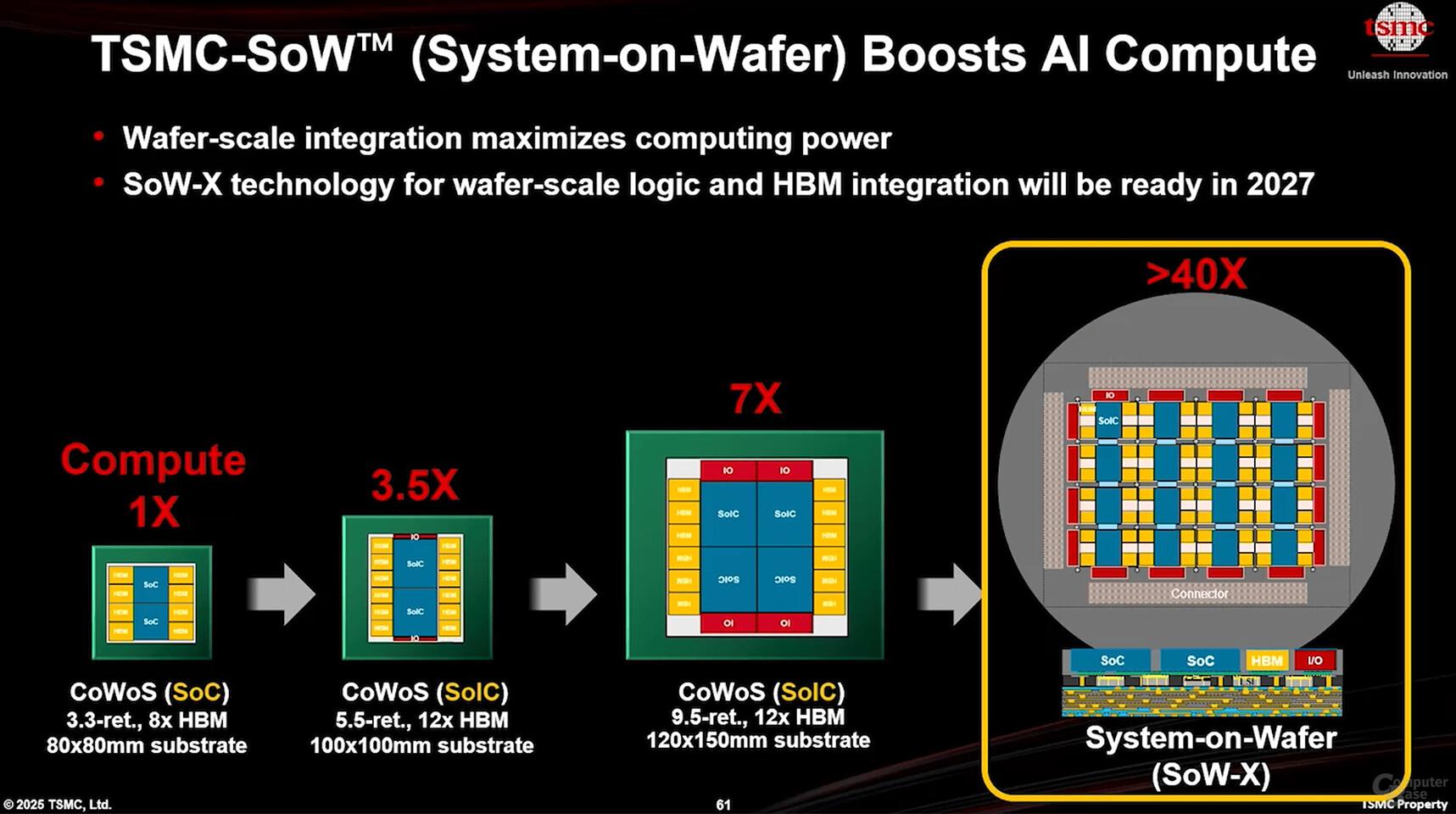

Cela dit, TSMC ne mise pas exclusivement sur CoPoS. L’entreprise continue de faire évoluer la famille CoWoS avec ses variantes L et R (consultez cet article pour plus de détails sur ces conceptions), et développe en parallèle SoW (System-on-Wafer), une autre voie qui vise à tout intégrer directement sur un wafer unique massif, comme le note ComputerBase. Ces approches visent à répondre aux différentes demandes de cients, et bien sûr à repousser les limites actuelles de l’intégration.

© ComputerBase

Le site AP7 de Chiayi, dans le sud de Taïwan, a été désigné comme centre névralgique pour ces méthodes de packaging de prochaine génération. C’est là que seront produits les modules CoPoS à grande échelle (les lignes pour CoWoS resteraient à AP8). NVIDIA serait l'un des premiers partenaires de lancement : l’entreprise espère intégrer jusqu’à 12 modules HBM4 avec plusieurs chiplets GPU pour ses futures puces IA, selon des informations rapportées par TechPowerUp.

| Un poil avant ?Test • WD_Black SN8100 (SM2508 + TLC 218L) | Un peu plus tard ...Advancing AI 2025 : AMD dévoile ses plans pour l’IA et les serveurs jusqu’en 2027 |  |