BiCS-5 : Toshiba et WD préparent déjà la NAND 3D 128 couches |

————— 08 Mars 2019 à 10h15 —— 14711 vues

BiCS-5 : Toshiba et WD préparent déjà la NAND 3D 128 couches |

————— 08 Mars 2019 à 10h15 —— 14711 vues

Alors qu'on est tout de même encore pas mal gâté de NAND 64 et 72 couches et que 2019 est en assez bonne voie pour être l'année des 96 couches, Toshiba et Western Digital ont évidemment déjà leur regard vers un futur (proche) fait de NAND 3D 128 couches ! Chez les deux intéressés, on parlera naturellement de NAND BiCS, ainsi les futures puces seront assez logiquement nommées BiCS-5. Il faut noter qu'en dépit d'une densité supérieure à 33% par rapport à la BiCS-4, la future BiCS-5 sera de type TLC avec 3 bits par cellule et fera l'impasse sur la QLC et ses 4 bits par cellule, pourtant plus récente. Ce serait là certainement l’aveu de rendements toujours pas bien faramineux de la production de NAND QLC; après tout, les rendements de la NAND TLC introduite en 2009 n'ont réellement décollé qu'au début de 2018, il n'est donc pas impossible à ce que la NAND QLC nécessite également plusieurs années avant d'atteindre à son tour des rendements digne de ce nom.

![Si vous cliquez, vous cliquez. bics 5 [cliquer pour agrandir]](/images/stories/_stockage/ssd/toshiba-wd-bics-5-architecture_t.jpg)

Pour rappel, en août 2018, il se susurrait qu'Intel/Micron avaient justement du mal obtenir plus de 50% de NAND QLC pleinement utilisable, contre 90% avec la TLC, et ils n'étaient apparemment pas les seuls dans le milieu à rencontrer cette difficulté. Cela dit, on notera que la prédiction d'une hausse des prix qui avait alors accompagné cette rumeur ne s'est pas réalisée entre-temps, tout au contraire !

![Si vous cliquez, vous cliquez. Capacité en To estimée par wafer de 300mm [cliquer pour agrandir]](/images/stories/_stockage/ssd/toshiba-wd-bics-5-capacite-par-wafer_t.jpg)

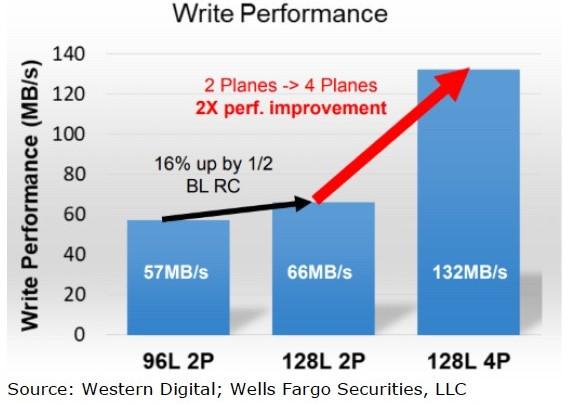

De retour à notre BiCS-5 bien culottée, cette dernière sera construite selon une architecture en 4 plans - à comparer aux 2 sections de la BiCS-4 - et chaque niveau pourra être accédé indépendamment des autres. En théorie, les performances en écriture seront ainsi doublées en passant de 66 Mo/s à 132 Mo/s par canal. Le die de la puce BiCS-5 utiliserait aussi la technologie CuA ou Circuitry under Array, une manière innovante de placer les circuits logiques dans la couche la plus basse sur laquelle viennent ensuite s'empiler les cellules de données, permettant d'économiser 15% de taille de puce. Tout cela semble bien prometteur, mais il faudra patienter encore un peu, la production commerciale n'était en principe pas attendu avant 2020, puis en 2021 ce serait au tour de la NAND 140+ couches d'entrer en jeu ! Et après, on verra... (Source)

Toujours vers le haut !

| Un poil avant ?Un boîtier avec une griffe d'originalité chez Aerocool ? | Un peu plus tard ...Afterburner enfin passe en version 4.6.0 finale |  |