Hard du Hard • Technologies de Mémoires — partie 3/3 |

• 22 Septembre 2023

Hard du Hard • Technologies de Mémoires — partie 3/3 |

• 22 Septembre 2023

Plus proche du processeur, le bus mémoire a longtemps été réservé à la mémoire vive : la RAM a été le facteur limitant de l’électronique pendant la majorité de son histoire. Utilisée pour les calculs, l’exploitation du système, mais aussi par l’affichage et le contrôle de différents périphériques, la RAM avait besoin d’être facilement et rapidement accessible. Historiquement, on a un bus système sur lequel sont reliés le bus mémoire et le bus entrée/sortie (southbridge vu précédemment). Mais très vite, on a besoin de plus de hiérarchie. Le CPU se voit relié de point à point au contrôleur mémoire (le northbridge), lui-même gérant l’accès au bus mémoire (prioritaire) et au bus interne qui dispose de son propre contrôleur d’entrée-sortie (secondaire) qui se partageront ce qui reste du débit. Et vraiment, la RAM ça demande un sacré débit. Pour accomoder ce débit, on a physiquement commencé à intégrer ce northbridge au sein de la puce du CPU dès le début des années 2000.

On a vu précédemment comment marchait la RAM. Et à la base, c’est en fait assez simple : on soude une puce de ram, qu’on relie aux pins de sortie du bus mémoire du processeur qui a besoin de cette RAM. C’est peu compliqué à faire, mais ça implique qu’il ne sera pas possible d’augmenter cette RAM après-coup. Dans la plupart des dispositifs électroniques, cette limitation n’est pas un problème.

Pour les PC, et principalement quand la RAM était le facteur limitant, ça voulait dire que le matériel devenait obsolète très vite. Pire : si on voulait augmenter la RAM à la conception du système, il fallait mettre beaucoup de puces. Donc prendre beaucoup de place sur la carte-mère. À partir de 1982, l’invention du module mémoire en ligne permet de simplement ajouter un connecteur à 60 contacts (dont la moitié étaient redondants) pour venir connecter un Single Inline Memory Module (SIMM) qui pouvait atteindre les 16 mégaoctets de capacité de DRAM. Pour cela, ils combinaient un bus d’adresses large de 24 bits, un bus de données de 8 bits et deux lignes d’alimentation. Une seconde version à 144 contacts (redondants) de 32 bits de données permettra de monter à 128 Mo de capacité. Ces deux bus parallèles tournent au rythme de l’horloge interne transmis par les signaux strobe.

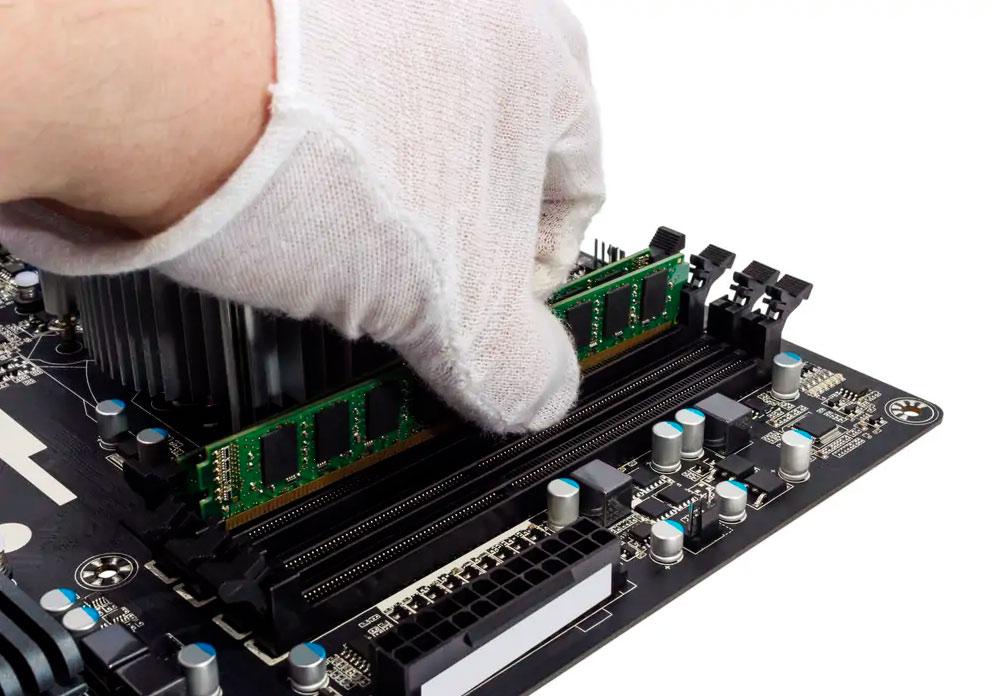

![Visionner en grand sur un magnifique pop-up A poil le PCB ! [cliquer pour agrandir]](/images/stories/articles/ram/ddr4/gskill_ripjaws_4/gskill_ripjaws4_ddr4_cl15_nue_t.jpg)

Un module DIMM de SDRAM DDR4 de chez G.Skill

Lorsque les processeurs 64 bits (lire : des processeurs au bus mémoire de 64 bits de large) prirent leur envol dans le début des années 90, il fallait donc deux SIMM de 32 bits pour occuper les bus mémoires. En abandonnant la redondance des contacts des SIMM, il a pu être possible de doubler la largeur du bus de données. Ce nouveau format s’appelle le Dual-Inline Memory Module.

Le DIMM, comme le SIMM avant lui, sont normalisés par le Joint Electron Device Engineering Council (JEDEC), une organisation des principaux fabricants de composants discrets et de circuits intégrés. Alors que l’informatique domestique décolle et que le monde s’équipe en systèmes d’exploitation qu’il faut ergonomiques, il faut plus de capacité et moins de latence dans la mémoire. Premièrement, au niveau des puces mémoire, on passera deux bits dans chaque ligne par période d’horloge : le Double Data Rate.

Rare photo de Mikael Jackson en train d'insérer une barrette de RAM OEM sur une mobo

Ces nouveaux standards DDR (commercialisés à partir de 2000) permettront à chaque fois de faire évoluer le standard des DIMM pour permettre plus de bits d’adressage, donc plus de capacité maximum. La génération DDR permettra des modules de 1 Go, la génération DDR 2 de 8 Go, La DDR3 de 16 Go, la DDR4 de 64Go et la DDR5 de 512 Go. Les vitesses du bus de transfert de données passeront de 12.8 Gb/s pour la DDR à 460 Gb/s pour la DDR5 avec des fréquences d’échantillonnage atteignant les 7.2GHz, ce qui est très exigeant pour un bus parallèle devant passer par des éléments électromécaniques hors des puces.

Cependant, la RAM n’est pas le seul à être greffé sur le northbridge. Dès 2003, un nouveau bus s’invite à la table. Descendant du Peripheral Component Interconnect, un bus parallèle traditionnellement branché sur le southbridge et largement utilisé pour les cartes d’extension, arrive le PCI Express.

Comme son nom l’indique, le PCIe est un bus destiné à relier des cartes d’extensions (des périphériques). Jusque là, il existait le bus PCI, qui avait le grand avantage de ne pas faire passer le trafic d’une carte d’extension à une autre par le processeur, ou le bus ISA, ou encore le port AGP, dont la vitesse de transfert pouvait monter jusqu’à 16Gb/s.

Le PCIe est, comme le SATA, une évolution de ces bus parallèle vers un bus série. En effet, porté à ce moment par l’évolution des puces, on maîtrise de mieux en mieux les liens série et on commence à pouvoir exploiter aux mieux leurs propriétés à hautes fréquences.

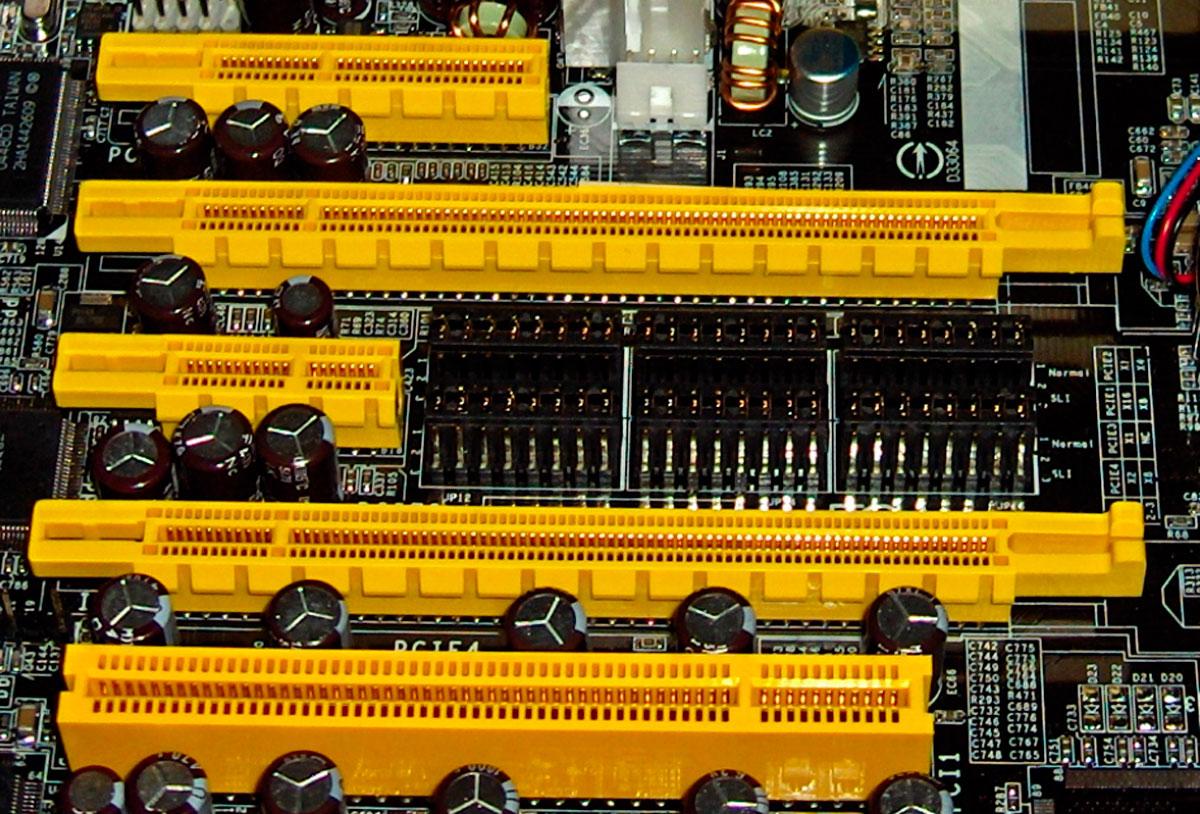

La norme PCI Express, maintenue par le PCI-SIG combine transfert de données et alimentation électrique. Son interface standard est un connecteur de bord de carte soudé sur la carte mère et qui peut accueillir une carte-fille adaptée. Ce connecteur possède une encoche entre la broche 11 et 12. Après cette broche, le connecteur existe en quatre tailles. Le plus petit, x1, possède 7 broches de plus pour un total de 18. Le x4 va jusqu’à 32 broches, le x8 va jusqu’à 49 broches et le x16 en a 82. Ces broches peuvent être des grounds, mais aussi des pins d’alimentation ou de détection de la taille de la carte, et bien sûr des lignes de transfert de données du bus PCIe. Ces x1 à x16 correspondent au nombre de lignes de transfert de données, chacune d’entre elles étant composée de deux paires différentielles, une pour chaque direction. Il est à noter qu’une carte plus petite peut s’insérer dans un connecteur prévu pour plus grand sans baisse de performances. Ainsi, une carte x4 peut rentrer dans un connecteur x16.

Des (vieux) connecteurs de BUS PCI et PCIe garés sur l'autoroute des pistes

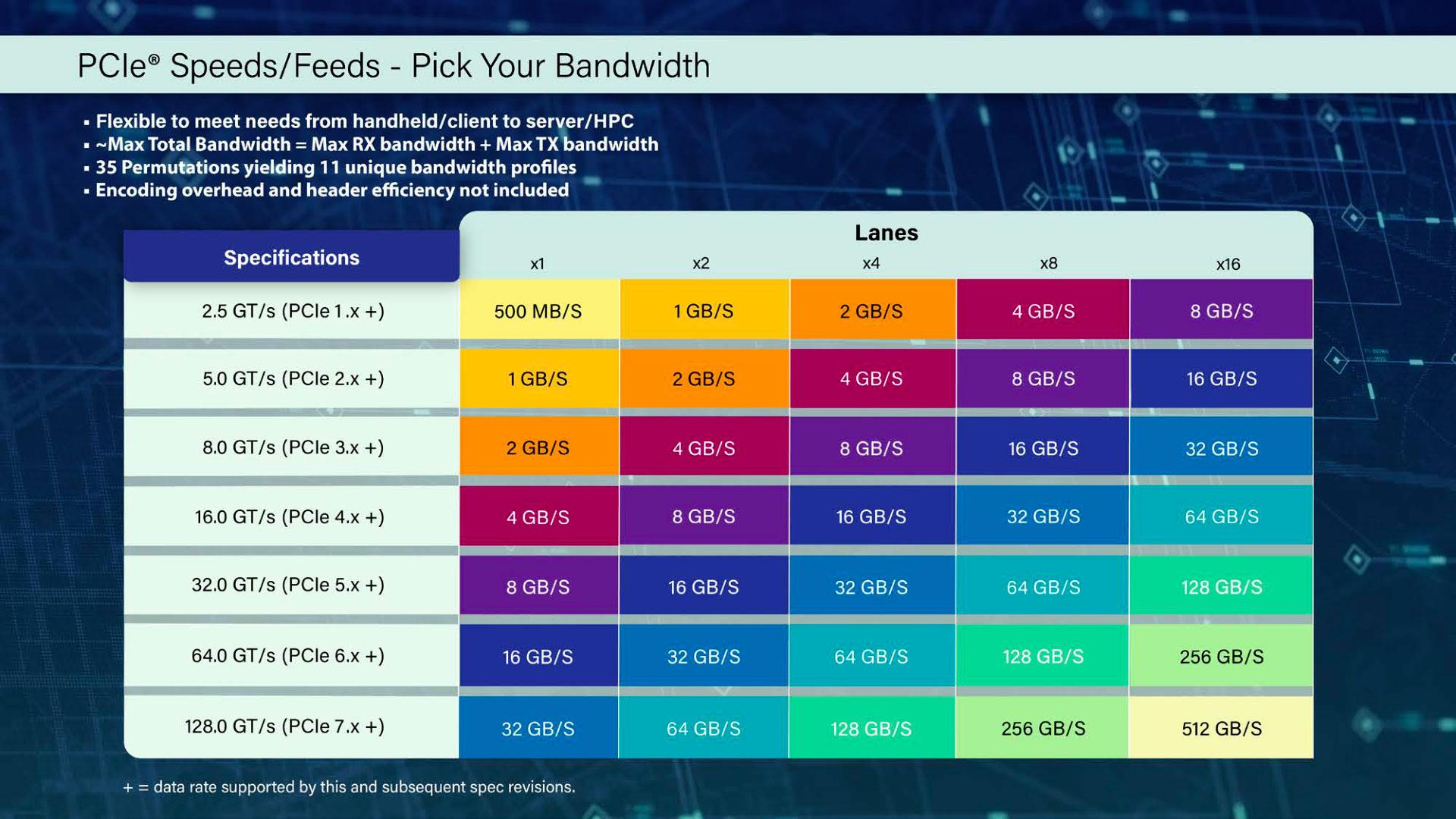

Le PCIe a été introduit avec une vitesse de transfert de 2,5Gb/s (encodé en 8bit/10 bit) par ligne, soit près de 40Gb/s avant encodage pour une connectivité x16. La version 2.0 a doublé ce débit, la version 3 l’a porté à 8Gb/s avant encodage (encodé en 128b/130b) par ligne, la version 4 a doublé ce débit et la version 5 l’a porté à 32 Gb/s. Le PCIe 6.0, sorti en 2022, est le premier à passer du codage NRZ à une modulation d’amplitude sur 4 niveaux (PAM4) pour augmenter la vitesse de transfert sans augmenter la puissance du signal. Toutes ces versions sont rétrocompatibles, mais sont limitées par la vitesse de transfert par ligne du plus bas standard du PCIe des composants : carte mère ou carte fille.

La feuille de référence des débits du PCIe

Il existe d’autres connecteurs standards pour le PCIe, comme les interfaces MXM utilisées dans les PC portables ou les PC industriels. Il existe aussi d’autres connecteurs dans le standard PCIe : le PCIe Power, par exemple, qui est un connecteur de puissance à fils sertis, proche du microfit mais avec des fils en plus pour pouvoir permettre la communication entre l’alimentation externe et de la carte fille.

Pour une application mémoire, généralement on n’aura pas besoin de ce surplus de puissance. Depuis quelques années, le PCIe est devenu un bus majeur pour les mémoires avec l’apparition des NVMe. Ces SSD branchés en direct sur le bus mémoire (plutôt que le but I/O comme un SSD SATA) vont pouvoir être accédés plus facilement par le CPU. Notons aussi le CFExpress, qui est en fait un bus PCIe déguisé !

Mais plus généralement, et j’aimerais attirer votre attention là-dessus, c’est qu’en réalité, on peut faire passer du signal PCIe dans n’importe quelle interface, tant que vous faites des paires différentielles et n’avez pas trop de pertes à la fréquence de transfert. Vous y gagnez en liberté de conception, mais évidemment ça devient moins interchangeable. Et ce PCIe, du coup, est devenu très largement utilisé au-delà du PC.

Mais bon, on sait bien pour quoi ça a été fait à la base, le PCIe.

Alimenter un écran en données, c’est quelque chose de titanesque. On s’en rend assez peu compte, puisqu’on est habitué à regarder des vidéos en streaming malgré des débits médiocres, mais on triche : on fait faire un boulot de décodage de gros plats de couleurs en image cohérente par notre processeur. Alors que l’écran, lui, a besoin de savoir, 24/60/120 (ou plus) fois par seconde s’il doit allumer chacune des 3 LED ou cristaux liquides de chaque pixel de sa dalle. L’unité de calcul vidéo va donc devoir envoyer beaucoup de données, qu’elle va devoir calculer à partir de sa programmation.

Initialement, pour l’affichage, on utilisait tout simplement une portion du CPU et de la RAM. On peut aussi utiliser des microcontrôleurs des SoC, bref, afficher demande du débit, mais n’est pas dur. Si c’est pour afficher l’heure, l’unité de calcul va avoir besoin des chiffres et du format de l’heure. Si c’est pour afficher Night City dans Cyberpunk 2077, elle va avoir besoin de plus d’informations que ça. Elle va nécessiter beaucoup, beaucoup de puissance et de mémoire. Pour les gamers, évidemment, mais aussi pour tout ce qui est de l’édition vidéo, de la 3D, du calcul en parallèle, de l’IA, etc.

Des composants ont donc été créés pour éviter d’avoir à utiliser de la RAM et du CPU quand on veut afficher des objets complexes. On va avoir un processeur graphique (GPU) et de la mémoire graphique. Le processeur graphique reçoit du CPU les informations dont il a besoin par son interface de bus, l’envoie au contrôleur de mémoire graphique, qui communique avec les cœurs du processeur eux-mêmes. Enfin, le processeur envoie le résultat au bus graphique, par d’autres interfaces (VGA, HDMI, DP, etc) qui alimentent les affichages en données.

![3N C11QU4N7 C357 P1U5 6r4ND Diagramme GA104 [cliquer pour agrandir]](/images/stories/articles/gpu/ampere/rtx3070/founders_edition/diagram_ga104_t.png)

![3N C11QU4N7 C357 P1U5 6r4ND photo détaillée d'un CPU AMD Renoir pour desktop [cliquer pour agrandir]](/images/stories/_cpu/am4/amd_renoir_desktop_layout_t.jpg)

A gauche, une architecture de GPU, à droite de CPU. Le GPU est très fort pour le calcul parallèle.

La mémoire utilisée va être de la RAM avec un débit spécialement élevé pour pouvoir gérer à la fois le bus interface (PCIe dans les cartes graphiques) et le dialogue avec les nombreux cœurs du processeur graphique. On parlera de GDDR SDRAM, qui va avoir des bandes passantes encore plus élevées que la DDR, pouvant monter jusqu’à 1,3 Tb/s. C’est trois fois plus que la meilleure DDR SDRAM, avec une horloge plus rapide aussi, mais un prix aussi deux à trois fois plus élevé qu’une DDR SDRAM.

|

|

| Un poil avant ?2 ans de feuille de route CPU : ça va swinguer chez Intel (MAJ) | Un peu plus tard ...3200 $ pour une carte graphique. Ouais, quand même. |  |

| 1 • Préambule |

| 2 • Les Mémoires & vous |

| 3 • Mémoires hors-ligne modernes |

| 4 • Solid Snake Drive |

| 5 • |

| 6 • Une puce pour les rassembler tous ? |