Hard du Hard • Technologies de Mémoires — partie 3/3 |

• 22 Septembre 2023

Hard du Hard • Technologies de Mémoires — partie 3/3 |

• 22 Septembre 2023

Parce que c’est très bien ces mémoires, mais il faut quelque chose pour les lire et les écrire. Un genre de système informatique, qui saurait comment les décrypter. Et donc, un moyen de transmettre les informations. Je ne vais pas trop entrer dans la terminologie, mais on va parler ici de bus.

Prenons le modèle Open Systems Interconnection (ou modèle OSI) qu’on applique généralement pour les réseaux. Ce modèle conceptuel découpe les réseaux en 7 couches. Les 4 couches plus hautes (7, 6, 5 et 4) – les couches de l’hôte - vont se préoccuper des informations elles-mêmes. C’est du software, c’est pénible, je ne vais pas aborder ça ici. La couche 3 du Réseau et la couche 2 du Lien logique sont les couches du medium. Elles sont aussi logicielles, mais vont concerner directement les caractéristiques de la transmission du signal. La couche 1, la couche physique, va décrire l’interface qui permet la communication. Le lien logique va donc dicter la trame que la couche physique va transmettre.

Comparatif de bus (sans roues)

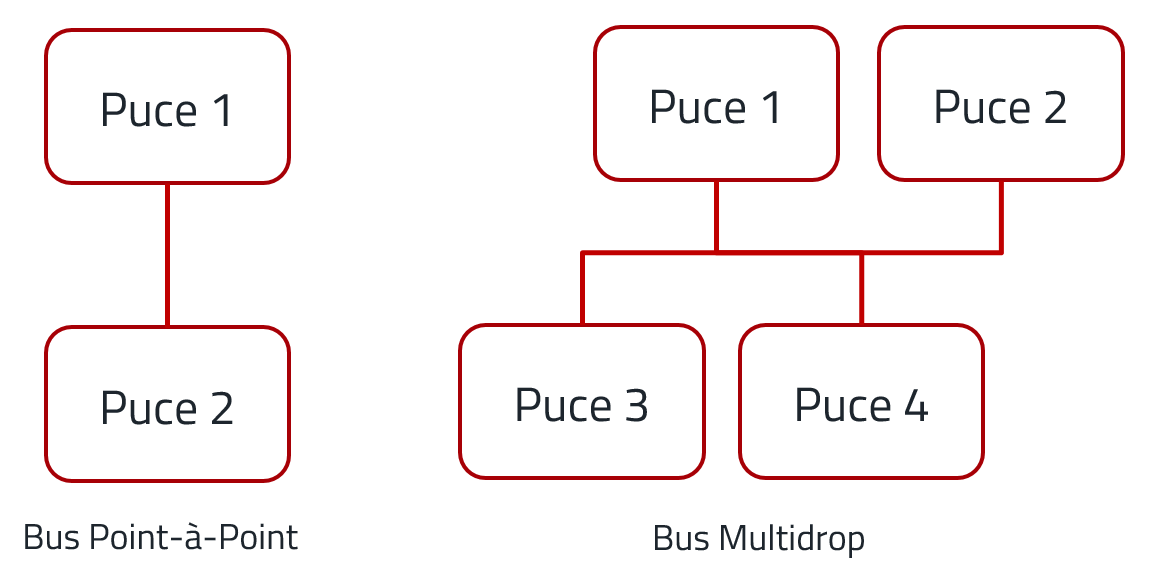

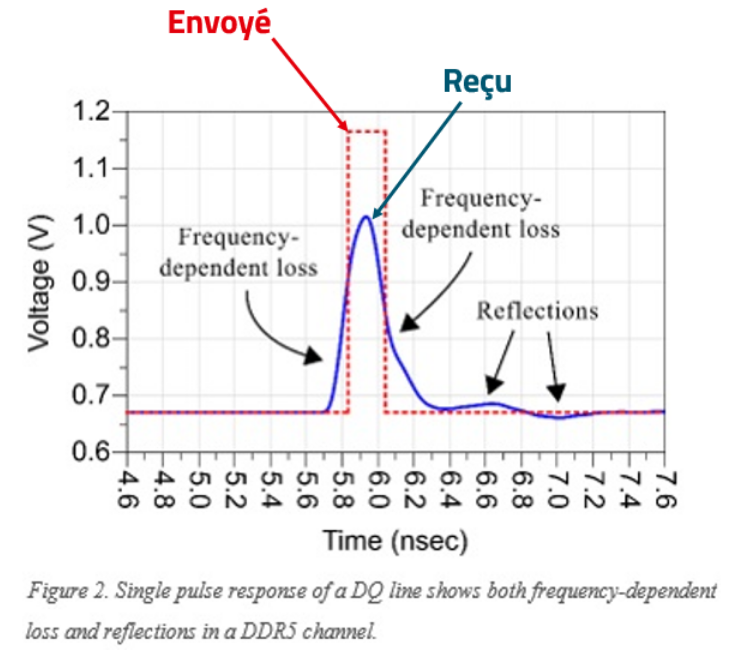

La couche physique va elle-même être composée de plusieurs lignes électriques, sur lesquelles passent des signaux, qui vont en général être des signaux rectangulaires sur deux niveaux ou plus. Ces lignes peuvent être reliées à un ou plusieurs composants, y compris des composants internes au sein d’une même puce. On appelle ça des bus. Le principal défi de ces bus est de garantir l’intégrité de l’information, et donc l’intégrité du signal rectangulaire envoyé par la puce pour qu’il puisse être reçu par une autre puce.

La différence entre le signal envoyé par une puce et le signal reçu par une puce enface (ici, de la RAM)

Le bus, c’est avant tout une topologie de réseau : tous les composants connectés au bus peuvent parler ensemble. Pas forcément avec les mêmes règles, mais en tout cas ils partagent le même medium. Parfois, il y a deux composants sur ce bus, mais ça peut monter à plus. Mais on a souvent besoin d’arborescence plus compliquée que ce simple segment : on va avoir besoin de faire un lien vers d’autres bus. Un lien pour faire passer les informations sous d’autres formes, peut-être.

Dans les microprocesseurs, vous avez en général un bus système, qui va donc déboucher sur un bridge I/O, qui va permettre de connecter des bus externes. Ainsi, ceux qui ont une bonne mémoire savent qu’une CompactFlash, un lecteur CD et un disque dur peuvent être connectés sur un bus IDE. Mais il en existe évidemment des plus récents, et des plus anciens.

Alors que les lecteurs de mémoires externes ou secondaires se multipliaient, il devenait nécessaire de trouver un bon moyen de relier le contrôleur de ces mémoires avec le southbridge du processeur. Dans l’architecture PC/AT (Personal Computer/Avanced Technology) IBM, ce fut Western Digital qui développa une interface nommée l’Advanced Technology Attachment. Pour IBM, WD et Compaq, l’objectif était d’avoir un bus qui fonctionne avec divers lecteurs de mémoire qui auraient des contrôleurs intégrés : des Integrated Drive Electronics (IDE). Ils utilisent donc le bus ISA 16 bits d’IBM pour relier le processeur à un contrôleur qui s’occupera de toute la partie de contrôle du disque (la vitesse de rotation, la position des têtes de lecture, etc.) qui était auparavant contrôlée par la carte-mère. Le bus IDE (ou ATA) devra donc seulement envoyer des adresses mémoires et envoyer/recevoir des données. Un standard industriel voit le jour en 1986.

Des périphériques IDE avec leur nappe + connecteurs (ce qui ne rajeunit pas)

Le bus IDE est un bus parallèle, raison pour laquelle il fut appelé rétrospectivement Parallel ATA (ou PATA). Sur les 40 conducteurs composant sa nappe et ses connecteurs, 16 vont transmettre les données, 7 seront des masses, 3 transmettront les adresses demandées, un sera inutilisé, et le reste servira à gérer les problèmes de priorité, de maitre-esclave ou autres. La transmission parallèle nécessite une bonne maitrise de la synchronisation des lignes, car la ligne 0 va envoyer le bit 0, puis le bit 16, puis le 32, la ligne 1 va envoyer le bit 1, puis le 17, etc. et le récepteur devra recevoir 0, puis 1, jusqu’à 15, puis ensuite à nouveau de 16 à 31, et ainsi de suite.

La transmission parallèle limitera la vitesse à ce que le système peut encaisser comme délai entre conducteurs de signal, mais aussi les interférences que font les conducteurs entre eux. Mais avec 16 lignes, elle peut faire passer 16 bits d’un seul coup. Dans le cadre de l’IDE, le signal ne montera jamais bien plus haut qu’un Gb/s pour une fréquence d’échantillonnage autour des 80MHz. Et encore : on pouvait avoir deux périphériques par nappe, qui devaient se partager le débit. Débit qui était aussi limité par celui du bus I/O du processeur. De toute façon, ce n’était pas très grave : les disques durs de l’époque ne poussaient pas plus de 600 Mb/s. Le bus IDE est souvent accompagné de divers connecteurs de puissance pour relier les périphériques internes à l’alimentation, comme des Molex 4 broches dans les alimentations d’époque.

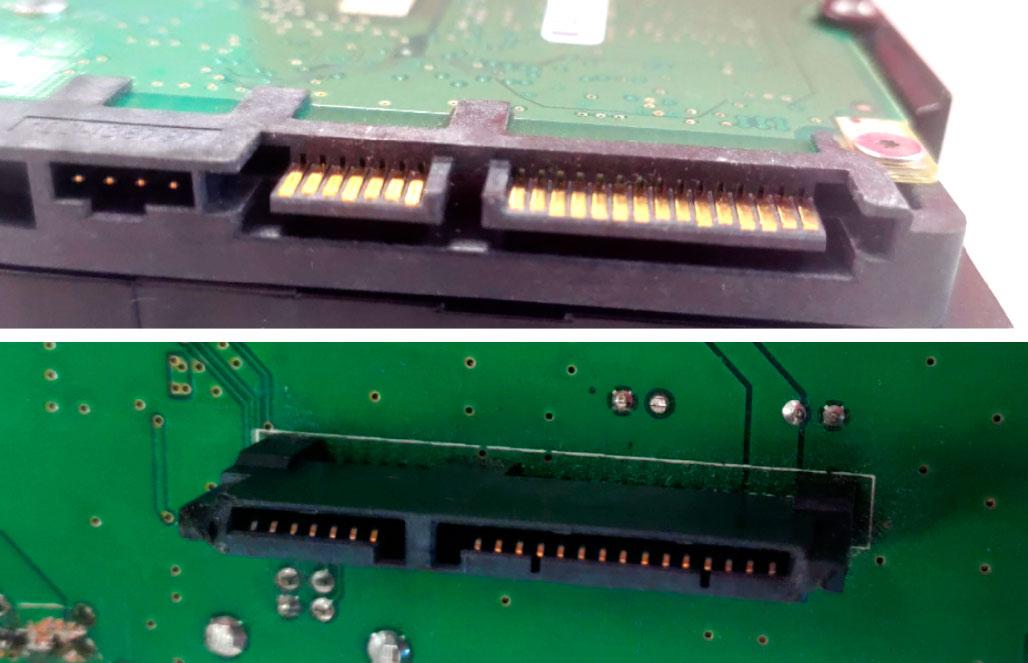

Le bus SATA, introduit en 2003 est un changement de paradigme par rapport à l’IDE. En effet, plutôt que de passer un peu de débit donné dans plein de lignes, on va passer un gros débit de données dans peu de lignes. En fait, on a deux lignes de transmission de données. Les lignes n’ont pas besoin de marcher de concert, car les données ne sont pas en parallèle. Elles sont en série, d’où le S de Serial ATA. Là où l’IDE utilise une grosse nappe de conducteurs, la connectique SATA ne va présenter que 7 contacts et le câble que 2 paires de signal (non-torsadées) et 3 fils de masse. On utilise ici la puissance de la paire différentielle, dont l’intérêt est de réduire les pertes de signal à haute fréquence, et donc de pouvoir passer par là même des signaux à plus haut débit. Les 3 fils de masse s’intercalent entre les paires différentielles pour que chaque fil de signal soit entouré de deux fils et ainsi avoir une impédance uniforme sur les lignes de signal. On appelle ça une configuration GSSG, qui permet de minimiser les pertes à haute fréquence.

Et ça marche, le bus SATA permet de passer jusqu’à 6Gb/s en théorie avec une fréquence d’échantillonnage de 6 GHz, un peu plus de 4,5 Gb/s en pratique à cause de son encodage 8 bits vers 10 bits, dans les deux sens, mais pas en même temps (half duplex) dans sa version 3. Les deux puces communiquent par signal différentiel à basse tension (LVDS), car l’encodage 8b/10b permet d’annuler le courant continu qui pourrait résulter d’une moyenne de symboles trop biaisée vers le 1 (-1,5V) ou le 0 (+1,5V). Ses versions 1 et 2 permettaient de passer 1,5 Gb/s et 3 Gb/s en théorie.

À gauche, port SATA. À droite, connecteur SATA Power.

Le bus SATA introduit aussi un connecteur de puissance, le SATA power, qui a une forme similaire et dont le standard permet 3 niveaux de puissance : 3,3V, 5V et 12V. Contrairement à l’IDE, par contre, le SATA ne peut être en liaison que point à point : on ne peut pas brancher plusieurs périphériques sur une nappe qui possèderait plein de sorties.

Ces deux bus représentaient la majorité des connectivités de stockage secondaire et externe dans nos ordinateurs de bureau ces 40 dernières années. Mais ils sont de moins en moins nécessaires : peu adaptés aux PC portables, les ports IDE ou SATA étaient souvent remplacés par des solutions propriétaires. Pour l’électronique moins exigeante, les bus I2C sont communs. L’émergence des architectures d’électronique construites autour de SoC utilisent aussi de plus en plus d’autres bus série – voire des bus souvent utilisés pour la connectivité externe, comme l’USB High-Speed Inter Chip. Pire, les périphériques mémoires sont en train de passer à la vitesse supérieure.

|

|

| Un poil avant ?2 ans de feuille de route CPU : ça va swinguer chez Intel (MAJ) | Un peu plus tard ...3200 $ pour une carte graphique. Ouais, quand même. |  |

| 1 • Préambule |

| 2 • Les Mémoires & vous |

| 3 • Mémoires hors-ligne modernes |

| 4 • |

| 5 • Vous reprendrez bien une petite barrette ? |

| 6 • Une puce pour les rassembler tous ? |