Le cap'tain PCI-SIG sort le foc : cap sur le PCI Express 7.0 |

• 14 Juin 2023 à 15h45 • 28970 vues

Le cap'tain PCI-SIG sort le foc : cap sur le PCI Express 7.0 |

• 14 Juin 2023 à 15h45 • 28970 vues

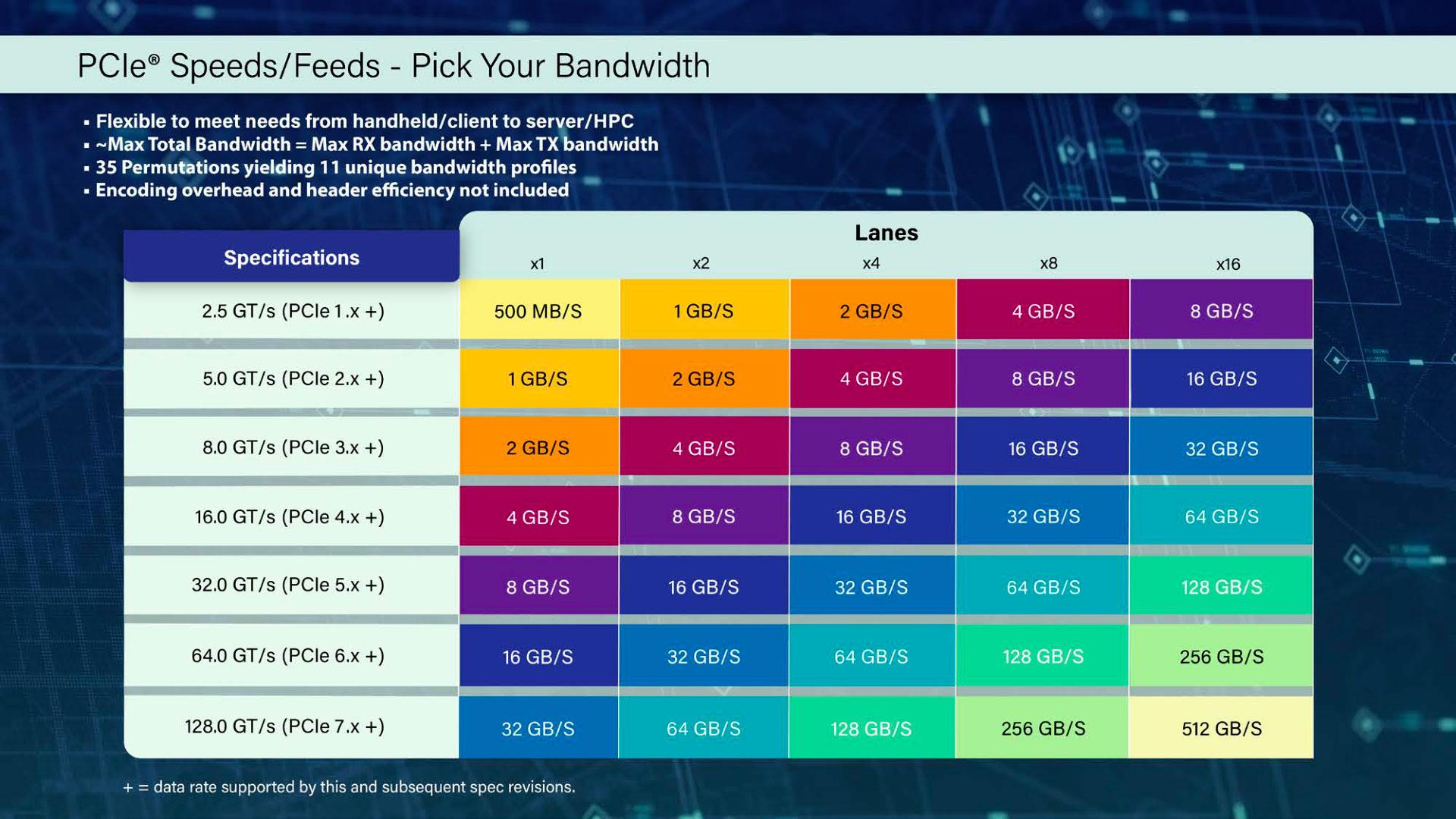

Alors que le PCIe 6.0 est attendu pour arriver sur nos machines en 2024, bien évidemment le PCI-SIG bosse en tâche de fond pour continuer à faire progresser la norme... et faire exploser les débits. Remarquez, les calculs sont vite fait pour ce qui concerne le bus PCIe : on double les chiffres à chaque génération. À l'occasion de son annuelle developers conference se déroulant actuellement à Santa Clara, le PCI-SIG publie son premier brouillon sur le développement du PCIe 7.0 et donne davantage de détails sur le PCIe 6.0 ratifié début 2022. La cadence amorcée avec le PCIe 4.0 continue donc de plus belle. Le PCIe 7.0 prévoit donc des débits à 32 Go/s pour une seule voie en full duplex, ce qui nous donne donc jusqu'à 512 Go/s avec un lien x16, toujours en full duplex.

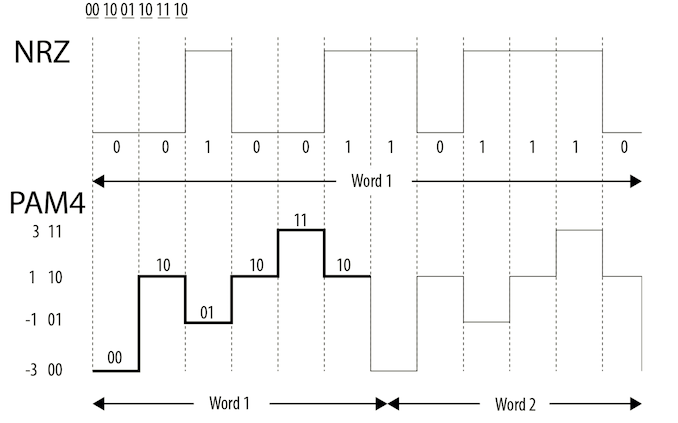

Rappelons que pour atteindre ce doublement de specs du PCIe 5.0 au 6.0, point de doublement de fréquence de fonctionnement mais une refonte du signal de modulation, passant du NRZ — modulation à non-retour à zéro — au PAM4 — modulation d'amplitude à 4 niveaux—. Le NRZ utilise 2 niveaux de signal pour représenter une valeur binaire, 0 (tension négative) ou 1 (tension positive), soit 1 bit par cycle. PAM4, comme son nom l'indique, utilise 4 niveaux différents chacun correspondant à 2 bits d'information logique (00, 10, 01 ou 11) et peut par conséquent faire transiter 2 bits par cycle d'horloge. En plus clair, pour la même fréquence on transporte deux fois plus de données :

Une modulation qui n'a rien de réellement de nouveau, déjà très utilisé dans les télécommunications, qui n'avait pas encore été adopté avant entre autres pour des questions de qualité de signal. L'arrivée du PAM4 est ainsi accompagnée de mécanismes de correction d'erreurs, FEC et CRC, et le PCIe 7.0 ne déroge pas à la problématique continuant d'utiliser l'encodage PAM4 + FLIT — consultez ce billet pour plus de détails — mais devant cette fois doubler la fréquence du bus pour atteindre ses objectifs, le portant à 30 GHz.

Des niveaux de débits qui sont encore loin d'être requis pour nous autres utilisateurs prolétaires du big data, mais qui par contre sont stratégiques pour ces derniers tels que les acteurs du machine learning, de l'IA, du cloud computing, du HPC ou encore les télécoms voire même dans les caisses à savon dont l'autonomie à des niveaux plus élevés demandera forcément plus de capacités de traitement. Rendez-vous en 2027 pour les premières solutions l'embarquant.

À noter également la ratification de specs pour le câblage interne et externe aux normes PCIe 5.0 et 6.0, utilisant les mêmes fréquences, qui devrait être présentée sur Q4 cette année. Oukilé mon riser PCIe 5.0 ?

Le cap'tain a encore 4 ans devant lui !

| Un poil avant ?Le G9 OLED en préco pour... Le même tarif que le G9 Neo (à sa sortie) ! | Un peu plus tard ...Intel confirme un nouveau branding pour ses processeurs |  |