Test • Intel X299 / Core i9-7900X & Core i7-7740X |

• 25 Juillet 2017

Test • Intel X299 / Core i9-7900X & Core i7-7740X |

• 25 Juillet 2017

C'est en août 2015 que Skylake a fait ses premiers pas via le Core i7-6700K, il aura donc fallut près de 2 ans pour le voir apparaître sur la plateforme haut de gamme du fondeur. Le passage chez Intel d'une architecture de la plateforme 115X vers 20XX se déroule généralement de la façon suivante : l'IGP disparaît, le nombre de cœurs, lignes PCIe et canaux mémoire croît et la fréquence est réduite. Pour le reste, l'architecture n'évolue pas (des fonctions boguées sur l’itération 115X sont parfois réactivées suite à un correctif) et on conserve donc une forte parenté entre les 2 gammes. C'est toujours le cas, mais quelques changement notables apparaissent cette fois, en particulier au niveau des caches, tant côté capacité que mode de fonctionnement.

Si côté L1, rien ne change avec toujours 2 x 32 ko dédiés respectivement aux instructions et données pour chaque cœur, ces derniers disposent par contre d'un L2 quatre fois plus large à 1 Mo. C'est donc une bonne nouvelle en apparence, si tant est que ce dernier soit aussi rapide, ce qui n'est pas forcément le cas. Second changement d'importance, le cache de 3e niveau est cette fois drastiquement réduit (de 2,5 Mo par cœur à 1,375 Mo) tout en abandonnant le fonctionnement inclusif (c'est à dire qu'il n'y a plus de copie systématique des données du L2 dans le L3). Son fonctionnement devient donc, à l'instar de Ryzen, de type victime (ou poubelle pour reprendre l'expression favorite de notre Titi) puisqu'il se remplit principalement par le biais des données éjectées du niveau 2.

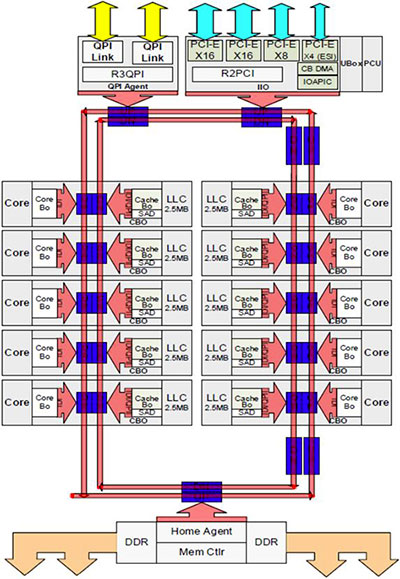

Mais le fonctionnement des différents caches n'est pas la seule modification notable, l'interconnexion entre les différents éléments du processeur évolue également fortement. Jusqu'à Broadwell-E, Intel utilisait un double bus en anneau (un par sens de circulation des données) permettant la connexion des cœurs, de leur L3, des contrôleurs mémoire et des liens de communication (PCIe, QPI). Ce mode de fonctionnement, également adopté il y a quelques années par ATi sur ses RADEON, permet des débits très importants, mais peut s'avérer délicat, et très coûteux en ressources, à mettre en œuvre lorsque le nombre d'éléments à connecter est important. Intel est par exemple obligé d'en utiliser deux en parallèle interconnectés entre eux pour les dies de plus de 10 cœurs.

Le double Ring Bus de Broadwell-E

C'est à cause de ce point particulier qu'est née Mesh, telle que la nomme Intel. Il s'agit en fait d'une matrice de connexion à 2 dimensions (lignes et colonnes) permettant de relier entre eux les différents éléments d'un processeur sur des axes de communication horizontaux et verticaux, par le biais de switches. Autant dire que la logique de gestion de tout cela est complexe, mais la solution semble apporter des bénéfices lorsque le nombre de cœurs est très important (comme dans le schéma ci-dessous) par rapport à la précédente interconnexion en anneau. Ce n'est par contre pas le cas pour un décacore et cela ne sera donc pas sans déconvenue comme nous allons le voir lors des tests, les avantages de Mesh ne contrebalançant pas ses inconvénients avec "si peu de cœurs".

![Ne pas appuyer ici mesh t [cliquer pour agrandir]](/images/stories/articles/cpu/skylake_x/mesh_t.jpg)

Représentation schématique de Mesh

Turbo Boost Max 3.0, qui avait fait son apparition avec Broadwell-E, bénéficie également d'une mise à niveau : il s'agissait d'un Turbo opportuniste permettant d'affecter (gestion au niveau de l'OS) le meilleur cœur de chaque CPU (qui varie d'un processeur à l'autre) au processus actif tout en lui permettant d'atteindre une fréquence plus élevée qu'à l'accoutumée (lorsque seul ce dernier était sollicité). Avec Skylake-X, ce n'est plus uniquement le meilleur cœur qui est concerné mais les 2 meilleurs, ce qui permet une mise en œuvre plus fréquente, surtout avec les OS modernes friands de processus en parallèle. On notera que le fonctionnement est à présent natif sous Windows 10.

Turbo Boost Max 3.0 mis à jour

Pour finir avec les nouveautés de Skylake-X, un mot concernant l'apparition des instructions AVX-512 (enfin d'une partie, certaines étant réservées aux puces de la gamme professionnelle) qui, comme leur nom le laisse deviner, permettent le traitement d'opérandes 512-bit. De quoi imaginer de jolis gains lors de leur prise en charge future par des applications permettant une telle largeur de calcul. Un mot sur Kaby Lake-X qui est également lancé en même temps que Skylake-X. Nos fidèles lecteurs se rappelleront que la différence entre les deux "architectures" est plus commerciale qu'autre chose : seul l'IGP ayant été modifié entre ces deux-là. Qu'est-ce qui peut donc les différencier sur une plateforme ne permettant pas l'utilisation de ce dernier ? Eh bien Kaby Lake-X se contente en fait de reprendre le die des Kaby Lake traditionnels en désactivant logiquement l'IGP. Il ne profitera donc que de 2 canaux mémoire et 16 lignes PCIe malgré une plateforme permettant bien plus avec un CPU ad hoc.

Résumé des apports de cette nouvelle plateforme

Résumé des apports de cette nouvelle plateforme

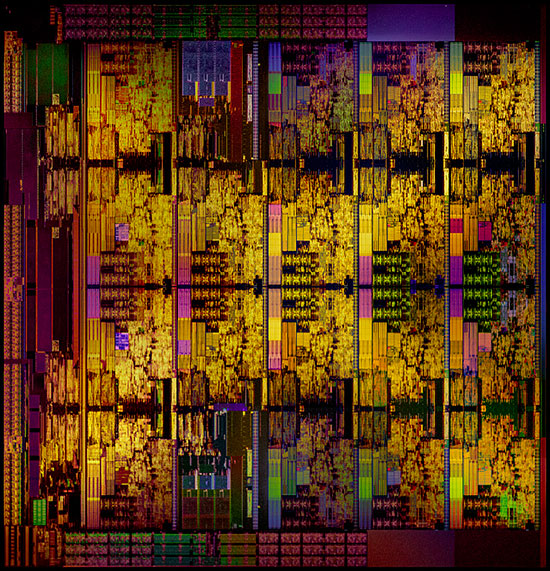

Pour terminer en beauté cette page, rien de tel qu'une petite photo de Skylake-X. On notera que l'image fournie à la presse ne représente pas le die de la version 10 cœurs que nous allons tester, mais à priori le sommet de la gamme à venir qui comptera jusqu'à 18 cœurs. Il semble également que 6 contrôleurs mémoire soient présents, mais la plateforme LGA 2066 n'en gérera que 4 en tout.

Die Skylake-X

Maintenant que nous avons rapidement décrit Skylake-X et son faux frère, passons page suivante aux processeurs reçus pour illustrer le comportement de cette nouvelle plateforme.

|

|

| Un poil avant ?Intel met des cerveaux dans une clef USB | Un peu plus tard ...Duel d'hexacores pour jouer, Ryzen ou Skylake-X ? |  |