La synthèse haut-niveau, un moyen d'optimisation des algorithmes ? |

————— 14 Janvier 2020 à 16h20 —— 10364 vues

La synthèse haut-niveau, un moyen d'optimisation des algorithmes ? |

————— 14 Janvier 2020 à 16h20 —— 10364 vues

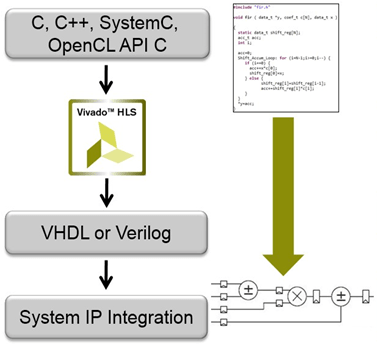

La synthèse haut-niveau, nous vous en parlions il n’y a pas si longtemps, fin août 2019. Le procédé, encore assez jeune, consiste à réaliser la synthèse automatique de matériel (via une description dans un langage très bas niveau nommé RTL, en général du VHDL) par traduction d’un langage plus haut-niveau comme le Java, C ou C++, enrichie d’annotations. Si cette pratique laisse sur le côté encore une bonne partie de l’optimisation — prétendez le contraire devant Guillaume, vous verrez le résultat — elle n’est pourtant pas si étrange qu’il n’y paraît.

En effet, bon nombre d’étapes de vérifications sont réalisées par simulation du code RTL sur différentes entrées, processus qui fait donc entrer en jeu du code haut-niveau. Ainsi, pour certifier un design en HLS, il suffit d’assembler des briques déjà prouvées et de prouver le code originel correspondant, ce qui est une étape qui, sans devenir pour autant anodine, réduit notablement sa complexité.

De plus, les performances ne sont pas toujours aussi horribles. Effectivement, des choix de design, coûteux en temps lors de rédaction à la mano, deviennent bien plus simples à effectuer par synthèse grâce aux annotations du code source. En clair, il est possible d’explorer une grande partie de l’espace des designs possibles à faible coût, une perspective juteuse pour l’industrie, d’autant plus que les start-ups cherchant à produire une puce doivent souvent décider d’un compromis en ce qui concerne la répartition de l’espace entre les différentes unités fonctionnelles, chose qui réclame à la fois une expertise en hardware, mais aussi en algorithmique, afin de trouver la partition optimale pour l’usage.

Dans le cas des applications de machine learning, très en vogue ces dernières années, le passage par le matériel peut même révéler des nouvelles manières d’exprimer le problème, qui se transposent également rétrospectivement sur les programmes sources. Parmi les optimisations possibles, il est question du passage d’une structure de données à une autre (flottant contre virgule fixe) ou de jouer sur les tailles de tableau (les puces préférant souvent les puissances de deux).

Pas évident de s’y retrouver en tant que simple consommateur, mais ces techniques évoluant vers une simplification de la conception du matériel est assez amusante à observer, et il est toujours curieux d’étudier les rouages internes des firmes qui produisent nos bidules électroniques en tout genre. À quand un kit "designer son ASIC soit-même" ? Avec le FPGA présent dans le dernier Mac Pro, certains en sont finalement plus proches qu'ils ne le pensent ! (Source : Semi Engineering)

| Un poil avant ?Nous avons essayé • Icy Dock TourghArmor MB839SP-B | Un peu plus tard ...Clap de fin pour Windows 7 pour le grand public, et après ? |  |

|