Intel fait une démonstration d'un Broadwell-EP avec FPGA intégré |

• 21 Novembre 2016 à 18h45 • 11766 vues

Intel fait une démonstration d'un Broadwell-EP avec FPGA intégré |

• 21 Novembre 2016 à 18h45 • 11766 vues

Le SC16 (Supercomputing 2016) est terminé, c’est un lieu où se déroulent des conférences et démonstrations sur des sujets comme la haute performance, le computing, le réseau, le stockage et l'analyse, bref ça envoie du bois. Dans le lot des présents, on trouvait Intel qui a racheté Altera il y a un peu moins d'un an, pour rapidement sortir le Stratix 10 à la suite. Voilà pour le contexte, passons à nos moutons et discutons processeur pour serveur. Comme vous le savez, les bonds en performance ne sont plus aussi impressionnants qu'avant, donc il faut bien trouver de nouvelles idées et c'est ce que l'on va voir à présent.

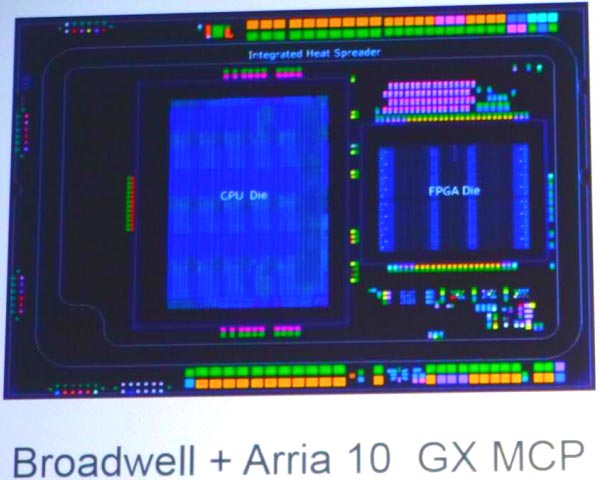

Durant cette démo, Intel a montré en action un Xeon E5 intégrant un FPGA Altera Arria 10, insistant d'ailleurs copieusement sur le fait que l'on n'avait pas affaire à deux entités distinctes, mais bien une seule et unique. En début d’année, il était noté que la partie CPU intégrerait quinze cœurs et que pour en arriver à une telle intégration, il était nécessaire d’utiliser plusieurs phases, une première nécessitant de placer la partie FPGA sur le même package que le CPU, puis de les fusionner pour en obtenir un seul élément. Le géant bleu a débuté ses travaux dès l’acquisition d’Altera puisque la bête utilise l’architecture Broadwell, et non pas Skylake (qui arrivera dans la seconde moitié de 2017, décalage grand public/serveur).

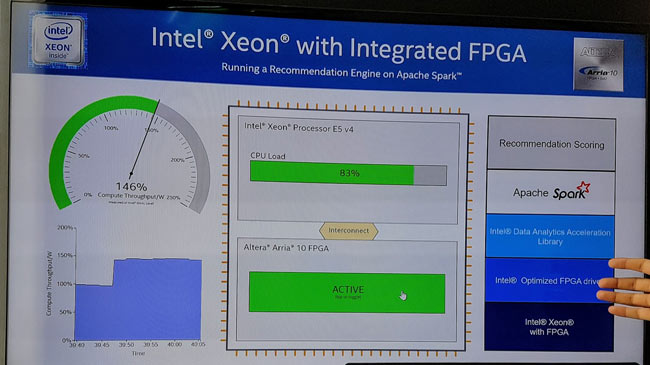

À présent, parlons performance, le géant bleu a montré comment ce duo pouvait permettre un gain en performance sur des tâches bien précises, en effet, les FPGA sont des puces reprogrammables et dans le cas d’Intel, elles sont utilisées comme des accélérateurs sans qu’il soit nécessaire d’en acheter ou d’en développer un en parallèle, réduisant ainsi les coûts et avec une consommation revue à la baisse. La démo utilise Apache Spark (un framework dédié au traitement des Big Data), on obtient une base de performance de 100% lorsque le FPGA est inactif, tandis que lorsqu'il est actif, les performances augmentent pour atteindre un peu moins de 150%.

Le graphique en bas à gauche montre le gain obtenu à l'activation du FPGA.

Cette démonstration montre que du côté des serveurs, des gains intéressants sont encore possibles (dans un usage bien spécifique), de plus, la technologie est concrète puisque des samples d'essai ont été envoyés, afin qu'ils soient utilisés par les développeurs et par certains utilisateurs en avant-première. Du côté du grand public, on peut se demander si on verra arriver ce genre de duo au sein de nos processeurs et si oui, avec quel gain à la clé ? (Source : diverses)