La nouvelle génération de FPGA en 10 nm est annoncée par Intel |

————— 03 Avril 2019 à 19h15 —— 17736 vues

La nouvelle génération de FPGA en 10 nm est annoncée par Intel |

————— 03 Avril 2019 à 19h15 —— 17736 vues

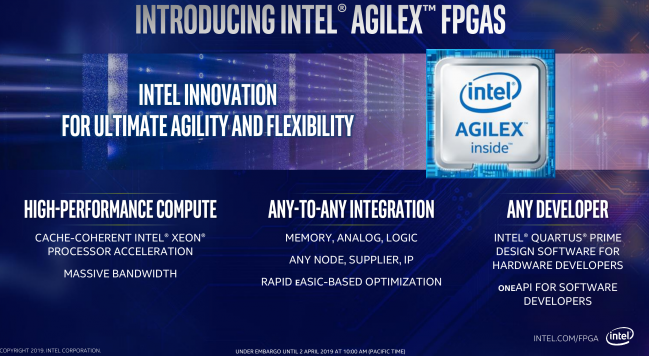

Parallèlement à la présentation de Cascade Lake en 14nm, Intel a également dévoilé plus en détail sa nouvelle génération de FPGA. Aperçue elle aussi à l'Architecture Day - en même temps, c'était le principe de la journée - sous le nom de code Falcon Mesa, ces derniers ont désormais un nom commercial et une date de sortie : ça sera Agilex et un début de sampling en mi-2019.

Niveau technologie, il s'agit cette fois-ci de 10nm FinFET de la firme, que l'on espère enfin en production de masse à cette période, on ne pourra pas dire que la firme n'a pas fait d'effort au niveau des nouveautés embarquées. En effet, les nouveaux bouzins pourront supporter dans leur version la plus chère de la HBM2, mais c'était déjà le cas de la génération précédente - Stratix 10 en déclinaison MX. Non, ce qui fait briller les yeux, c'est bien la prise en charge de la DDR5 et du PCIe Gen 5, ainsi que des modules Optane DC (quitte à les produire, autant les caser partout !). On signalera aussi des améliorations des DSP, des blocs logiques permettant désormais de réaliser des opérations en BFLOAT16, une modification du flottant pour les applications de Machine Learning.

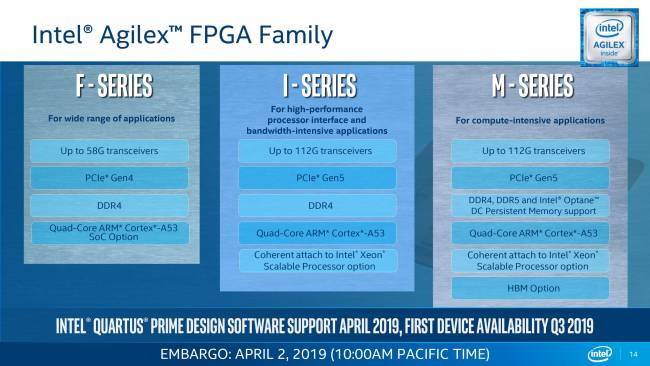

La gamme sera divisée en trois séries : en entrée de gamme les Agilex F, des SoC intégrant en option une partie CPU ARM Cortex-A53 à quatre cœurs accompagnée d'entre 392 et 2,6 millions d'éléments logiques supportant le PCIe 4 mais uniquement la DDR4 côté mémoire. Ensuite viennent les Agilex I, avec actuellement seulement deux modèles à 2,2 et 2,6 millions d'éléments logiques, mais qui passant en PCIe Gen5 pour doubler les débits par rapport à la version 4. Ces derniers pourront également être directement reliés à des Xeons par un Compute Express Link, designé pour être compatible avec les protocoles de cohérence de cache de ces puces. Enfin, la HBM, Optane et la DDR5 seront cantonnés aux chers Agilex M, dont les caractéristiques précises n'ont pas encore été dévoilées. Notons également la présence d'un transciver à 58 Gbps pour la série F et 112 Gbps pour la série I, de quoi envoyer sérieusement du pâté pour les applications de traitement de signal en temps réel. En outre, tous ces contrôleurs annexes seront rattachés par des chiplets - le fameux multi-chip-module - ce qui permettra de les graver à l'aide d'une finesse de gravure plus grande que le 10nm de la partie reconfigurable. Sans surprise, les liens entre chiplets sont réalisés via l'EMIB, l'interconnect à tout faire des bleus.

Si ce genre de produit n'est clairement pas destiné au grand public - bien que certaines applications puissent en théorie bénéficier d'une puce partiellement reconfigurable - il est toujours bon de voir Intel innover et diversifier ses sources de revenues en investissant sur des technologies axées professionnels. Et bientôt, ça sera au tour des GPU !

| Un poil avant ?X499 et X570 chez GIGABYTE | Un peu plus tard ...Mise à jour du dossier NH-U12A avec les mesures en Push et en Pull |  |

|