Des fuites sur Zen 5 et Zen 6. Vite du mastic ! |

• 29 Septembre 2023 à 15h55 • 39099 vues

Des fuites sur Zen 5 et Zen 6. Vite du mastic ! |

• 29 Septembre 2023 à 15h55 • 39099 vues

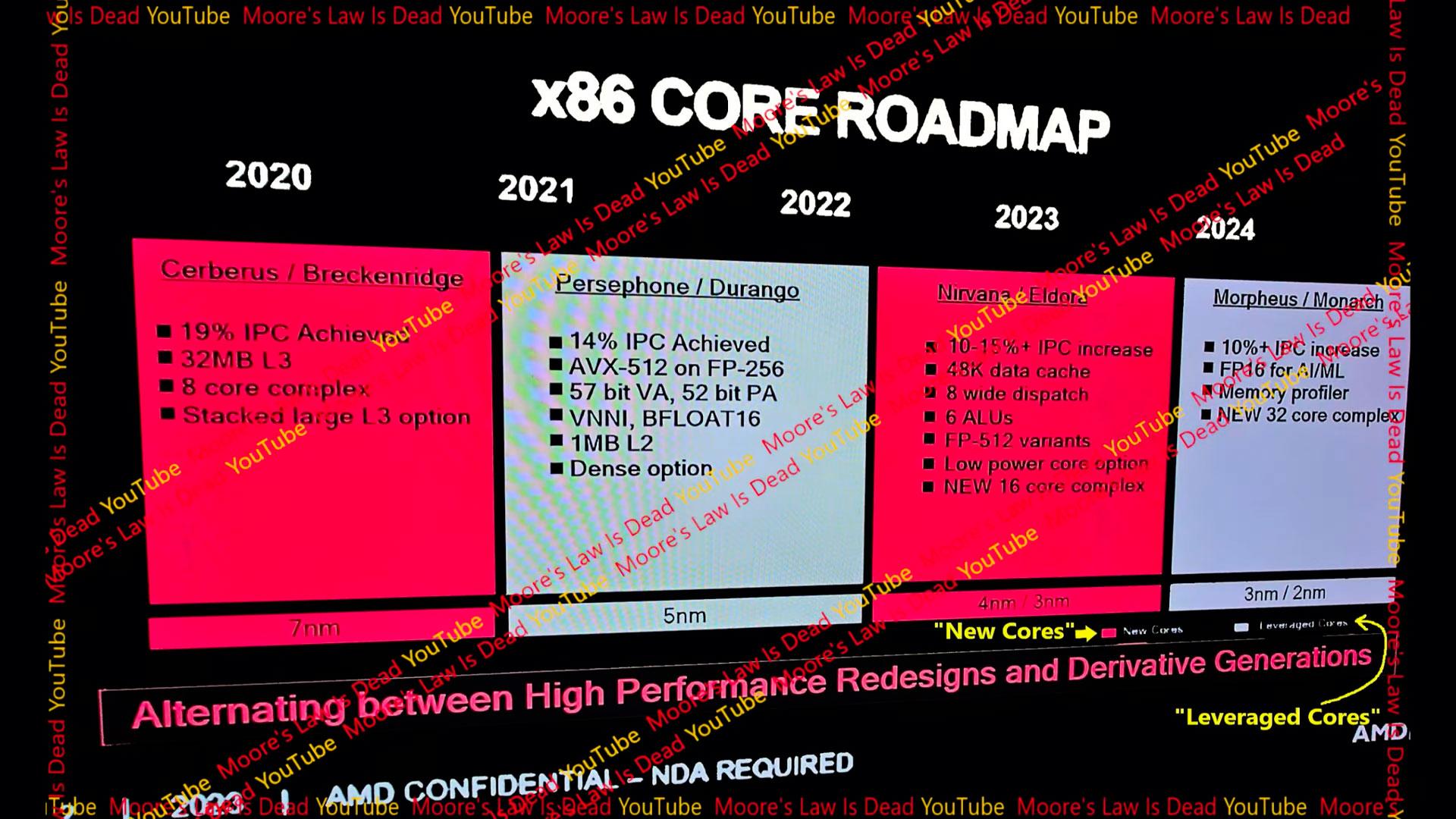

Alors que NVIDIA France subit les foudres de l'autorité de la concurrence, faisant au passage les gros titres un tant soit peu putputaclics (en plus de mal sourcer, m'enfin) soupçonnés de pratique anticoncurrentielle — tiens, c'est étonnant... Faudra qu'on vous raconte un jour quelques anecdotes, même si la présente affaire relève des activités liées au cloud computing — et bien figurez-vous que ça fuite chez AMéDé. Et ça fuite à propos du de « Nirvana » et de « Morpheus », aka Zen 5 et Zen 6, via deux pauvres screens de présentation interne. On y apprend cela étant 2- 3 trucs :

À propos des Ryzen 8000 nom de code top secret « Granite Ridge », attendus pour le premier semestre 2024, dont l'architecture se mue en big.LITTLE avec des performance core « Nirvana », similaires aux P-Core chez les bleus, qui devrait être gravés en N4P (node 4 nm TSMC) embarqués dans les CDD baptisés « Eldora ». Des CDDs que l'on l'on devrait également retrouver dans les prochaines puces « Turin » de la gamme Epyc. On ne connait pas encore le nom des cœurs basse consommation "Zen 5c", similaires aux E-Core chez les bleus, qui eux devraient être gravés en N3E (node 3nm TSMC).

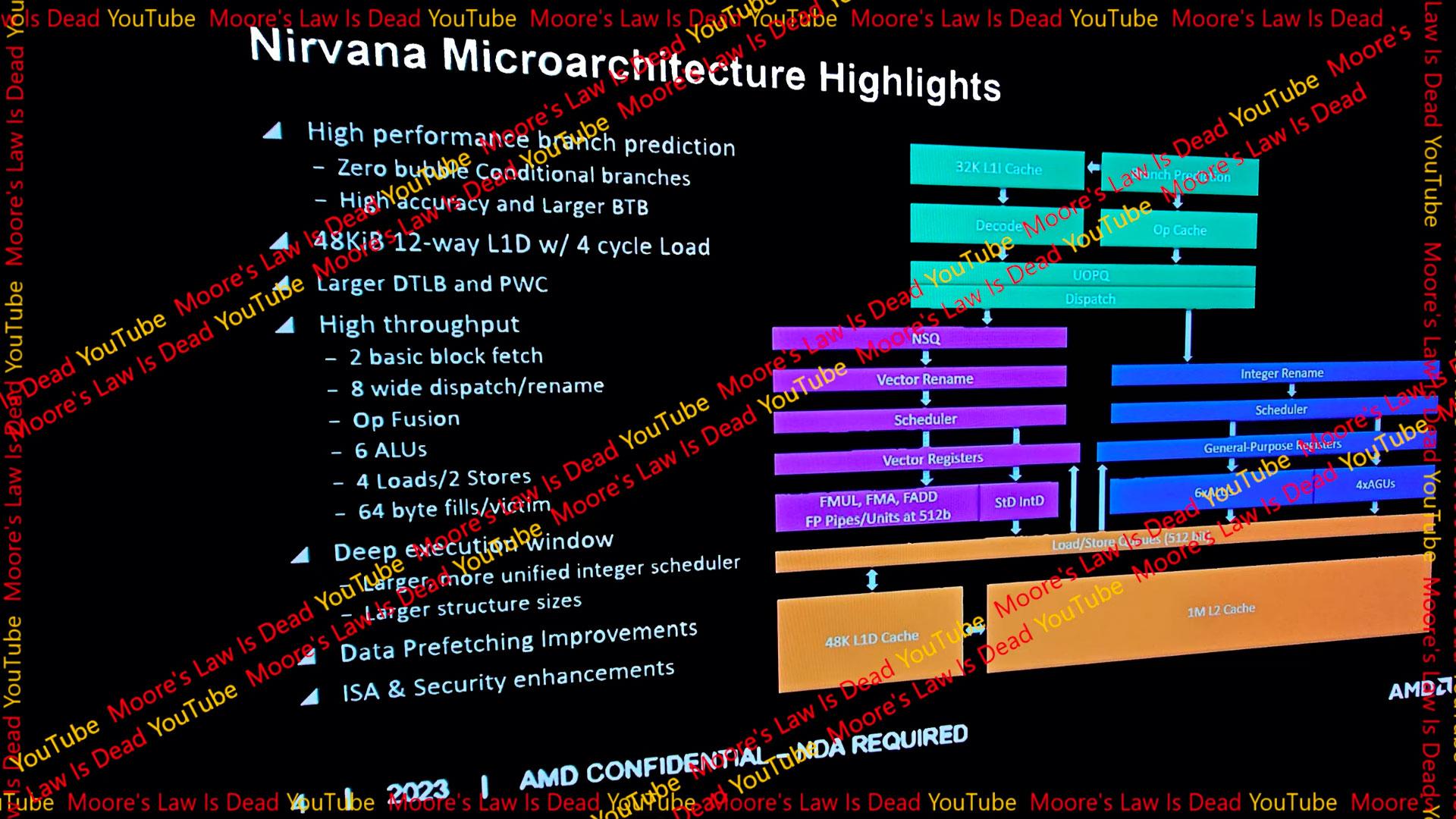

Si vous suivez, en substance, le gain d'IPC sur « Nirvana » est présenté pour être entre 10 et 15 % face aux cœurs « Persphone » de Zen 4. Le cache L1D ne serait pas en reste et prendrait 16 Ko passant de 32 à 48 Ko. Côté front-end, le débit vers le ROB (ReOrder Buffer) ou unités de disptach des micro-ops passerait lui de 6 (sur Zen 4 comme sur Zen 3) à 8 µOps / cycle d'horloge. Côté back-end, ce seraient 4 unités arithmétiques et logiques, les ALUs, contre 3 sur Zen 4, qui seraient déployées pour l'exécution des entiers. Enfin, chez les flottants, les registres FP / vectoriels passeraient à un adressage 512 bits. Des évolutions plutôt logiques au regard du passif de l'architecture Zen, qui n'accrédite pas vraiment le dit leak, et n'explique pas le gain d'IPC escompté.

Plus intéressant encore, le nombre de cœurs par CCX passeraient à 16, contre 8 sur Zen 4, sans savoir néanmoins si cette implantation ne concerne que les CCX hybrides ou basse consommation.

Sur Le lapin blanc « Morpheus » aka Zen 6, attendu lui pour le deuxième semestre 2025, AMD anticiperait une augmentation d'IPC moins ambitieuse de l'ordre de 10 % et des CCX de 32 cœurs profitant d'un passage à un node de gravure inférieur, et devrait intégrer des instructions FP16 dédiées IA ou machine learning. Le gros des changements devrait se situer au niveau du front-end et en particulier du prédicateur de branchements. Enfin, Zen 6 devrait également profiter d'un redesign du layout de la puce grâce aux « nouvelles techniques de packaging » permettant d'empiler CCD et IOD. (source à prendre avec des gants de boxe : Moore's Law iz déd)