Aux Chips Chaudes, Intel fait le point sur ses Météores |

• 23 Août 2022 à 17h15 • 18047 vues

Aux Chips Chaudes, Intel fait le point sur ses Météores |

• 23 Août 2022 à 17h15 • 18047 vues

En ce moment se tiennent les Hot Chips 34, une conférence dédiée aux progrès en matière de lithographie : il ne faut rien de plus pour voir le camarade Intel courir à l’événement. Si des conférences ont lieu en ce moment même concernant Meteor Lake, Arrow Lake, Lunar Lake ainsi que Ponte Veccio, les FPGA et les Xeon pour les pros, leur contenu n’a pas encore filtré jusqu’à nous, outre une présentation spéciale presse pas vraiment des plus détaillées.

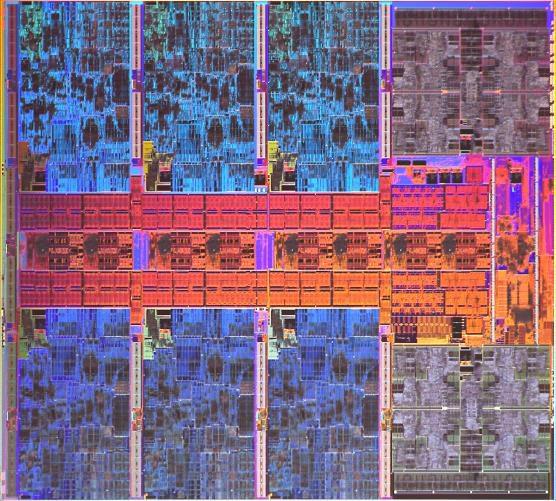

Si son contenu n’est pas des plus nouveaux, il est bon d’avoir un petit refresh (ahah) des attentes de 2023, avec la reconfirmation d’un die en Intel 4 pour le chiplet CPU de Meteor Lake, de N5 de chez TSMC pour le GPU (et non, il n’a jamais été question de N3 !), de N6 pour SoC et pour le die d’I/O (aussi nommé d’expansion dans les présentations). En outre, Intel confirme également que Meteor Lake utilisera Foveros (et non l’EMIB) : il s’agit d’un empilement 3D basé sur un interposer passif en 22 nm (metal layers uniquement du 22FFL, renommé Intel 16… pas facile de suivre). Une organisation proche de Lakefield, mais dans laquelle la distance entre connexions (ball pitch) a été améliorée pour atteindre 36 microns (contre 55 auparavant). Notez que ce die de dessous pourrait être actif si besoin est, mais le jeu n’en valait pas la chandelle sur Meteor Lake.

![Même pas cap' de cliquer Un schéma, c'est bien joli, mais sans légende... [cliquer pour agrandir]](/images/stories/_cpu/7nm_intel/intel-meteor-lake-die-hot-chips_t.jpg)

![Visionner en grand sur un magnifique pop-up meteor lake die locuza t [cliquer pour agrandir]](/images/stories/_cpu/7nm_intel/meteor-lake-die-locuza_t.jpg)

Si le seul schéma fourni par la firme ne nous apprend pas grand-chose de neuf depuis l’Intel Vision, au moins sommes-nous désormais certains des déclinaisons de Meteor Lake pour ce qui est du die de calcul. En effet, à cette précédente conférence, nous avions déniché un cliché du die en 2 +8 cœurs, Twitter en a fourni un autre en 6 +8 que nous retrouvons ici ; et les bleus nous ont confié que cette version n’était pas la plus testicouillue : de quoi laisser planer le doute sur la plus grosse configuration, probablement un 8 +16 à la Raptor Lake ?

Pour le reste, Intel essaye de pousser son écosystème UCIe (un standard de communication interchiplets de la firme, open sourcé, qui fait bien pensé à l’AIB déjà croisé) mais ne semble pas encore avoir de partenaire phare — peut-être via leur service de fonderies ? Enfin, puisque les chiplets sont de mise, les bleus peuvent désormais mixer ensemble leur porte-folio complet de produits : de quoi imaginer raisonnablement un Xeon + FPGA en chiplet dans un futur proche !

![Enlarge your pe...icture Et pour le futur des CPU bleus... [cliquer pour agrandir]](/images/stories/_cpu/intel-meteor-arrow-lunar-slide_t.jpg)

Et pour la suite : toujours plus de chiplets !