Puces et silicium 3D, des composants à court de jus ? |

————— 16 Septembre 2019 à 15h14 —— 12332 vues

Puces et silicium 3D, des composants à court de jus ? |

————— 16 Septembre 2019 à 15h14 —— 12332 vues

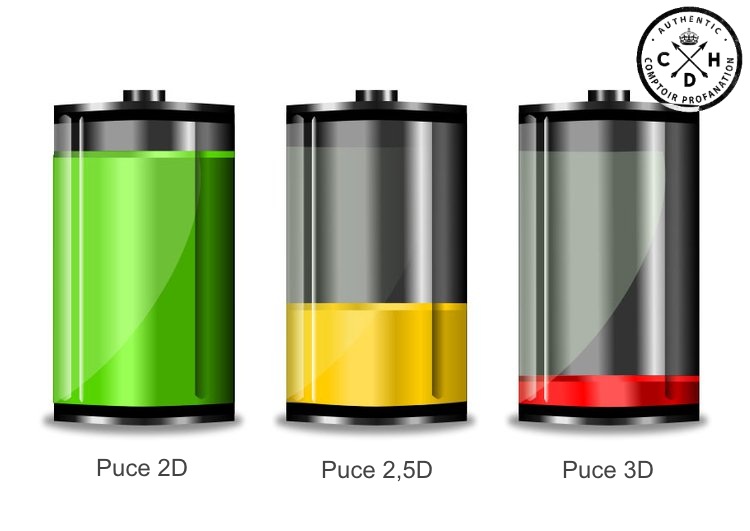

Faire évoluer les performances des puces informatiques n'est pas une mince affaire, et les différentes innovations sont loin d'être très simples à mettre en œuvre, tout comme les difficultés à faire décoller les mémoires HBM2. Même si les technologies d'empilage des couches de silicium pour réaliser des puces 3D et gagner en espace paraissent intéressantes, de nombreux soucis viennent s'imposer sur ces méthodes de conception. Entre les problèmes liés à la verticalité et ceux concernant l'empilement, la gestion de l'énergie pour les puces du futur ne parait pas si simple.

Selon Chris Ortiz - ingénieur chez ANSYS - l'évolution des puces vers la verticalité entraîne - logiquement - une augmentation du nombre de transistors, de grilles et de nodes ce qui rend de plus en plus dur de vérifier la répartition de puissance. Un des problèmes les plus récents consiste en la diminution de la tension de fonctionnement sans pour autant diminuer la consommation totale, ce qui augmente le courant moyen nécessaire. Avec la miniaturisation de l'espace, il va donc devenir de plus en plus dur de pouvoir fournir ce courant et, à terme, un compromis devra être fait. Cependant, le cher monsieur garantit que des améliorations sont possibles en utilisant la verticalité des circuits plutôt que de simplement empiler, permettant de transmettre de manière plus courte l'énergie entre les différentes couches, ce qui réduit l'impact des courants élevés sur les longueurs de piste.

D'autres éléments sont aussi impactés, comme le découplage des alimentations - qui permet une isolation entre les différentes puces - ou la gestion de l'enveloppe thermique. En empilant les différentes couches, il faut comprendre que l'isolation n'est pas aussi bonne qu’avant et par conséquent que les fuites sont possibles entre chaque épaisseur. La solution la plus efficace est de rajouter des couches d'interposer pour bien séparer chaque élément, mais l'impact sur le prix et la difficulté de conception est loin d'être négligeable. Le parasitage entre les parties numériques et l'alimentation en elle-même peut aussi s'avérer gênant, obligeant à porter une attention minutieuse aux résonances possibles. Finalement, cette introduction de chez SemiEngineering nous permet de mieux appréhender certaines difficultés qui entourent les tant réclamés circuits en 2,5D et 3D, montrant qu'en échange de cette technologie, des fonctions a priori simples peuvent devenir un challenge aussi difficile que l'amélioration de la finesse de gravure. (Source : SemiEngineering)

| Un poil avant ?Comptoiroscope • Borderlands 3 quand DX12 fonctionne | Un peu plus tard ...AMD : des nouvelles officielles pour Zen 3 et RDNA 2 |  |