Hard du hard • Anatomie du PCB d'un SSD |

————— 14 Janvier 2015

Hard du hard • Anatomie du PCB d'un SSD |

————— 14 Janvier 2015

Sur un air de Village Poeple in the navyyyyy, nous inaugurons avec grand plaisir ce nouveau type d'article, qui va peupler de plus en plus le Comptoir à l'avenir au sein de nos papiers habituels, afin de vous parler plus en détail du pourquoi du comment de certains compos. Commençons donc avec les SSD, ces fameux SSD dont nous vous parlons depuis leur arrivée sur le marché grand public, et qui auront été la dernière grande révolution matérielle de l'aire PCiste moderne. Du stockage ultra rapide prenant la relève de la, certes magnifique, mécanique des disques durs à plateaux et qui n'a pas manqué de faire couler beaucoup de transistors. Ça tombe bien, puisque cet article va vous expliquer comment sont foutues ces petites bébêtes.

Au début des années 1950, le mastodonte IBM chercha un moyen de stocker des informations binaires sur un support plus rapide et plus fiable que des bandes magnétiques, en place depuis des lustres. Plusieurs ingénieurs se mirent donc à plancher sur le problème, et ce fut Reynold Johnson qui présenta le premier son concept, le RAMAC (acronyme de Random Access Method of Accounting and Control) qui sera alors commercialisé en 1957.

![Enlarge your pe...icture ramdac_t.jpg [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/ramdac_t.jpg)

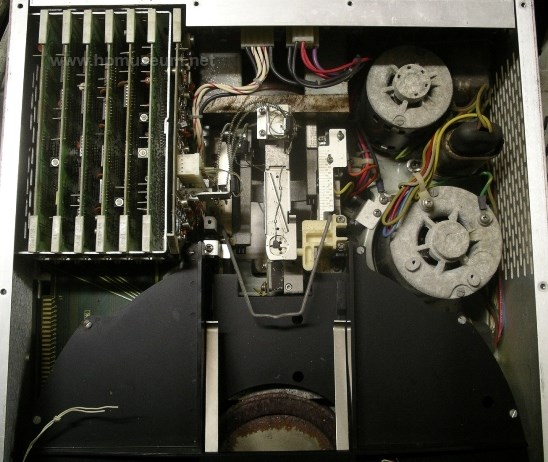

Un RAMAC entreposé au Computer History Museum

Il s'agissait d'un système de plusieurs centaines de kilos dont la capacité totale était de 5Mo. D'une consommation électrique gargantuesque, il était constitué de 50 disques métalliques de 61 centimètres de diamètre tournant à 1200 tours/minute, avec deux têtes de lecture/écriture qui pouvaient se déplacer verticalement d’un plateau à un autre en moins d’une seconde. Les bases de ce qui allait s'appeler « disque dur » étaient posées. Ce concept fut ensuite amélioré par IBM au fil du temps jusqu'à ce que HP sorte en 1970 le premier disque dur à tête mobile, capable de se déplacer sur 2 axes à la fois, donc sur la surface même du disque et non pas uniquement à partir de sa tranche. Ce sera alors un bras de fer technologique entre les quelques gros acteurs du secteur qui durera deux décennies.

Le HP-7900A, premier disque dur « moderne » sorti en 1971 d'une capacité totale de... 4,9Mo ! (c)HP computer Museum

Cependant, la taille de ces périphériques par rapport à leurs capacités de stockage resta problématique jusqu’au milieu des années 1990, quand il fut techniquement possible d'exploiter le phénomène quantique appelé magnétorésistance géante découvert en 1988 par 2 physiciens-chercheurs (dont un Français), ce qui leur vaudra d'ailleurs l'obtention du prix Nobel de physique en 2007. Sans rentrer dans le détail, c'est un phénomène qui fait que, pour un matériau exclusivement constitué d'une alternance de couches de fer et de chrome de seulement quelques atomes d'épaisseur chacune, il se produit un forte chute de résistivité sous l'action d'un champ magnétique. Grâce à cela, on est alors passé d'une densité de stockage de quelques dizaines à plusieurs centaines de Moctets par cm². Mais on savait depuis longtemps que le fonctionnement d'un disque dur reposant sur un principe mécanique et électromagnétique imposerait à terme une limitation des vitesses de transferts des données en lecture et écriture. L'avenir du stockage informatique se devait donc d'évoluer vers autre chose.

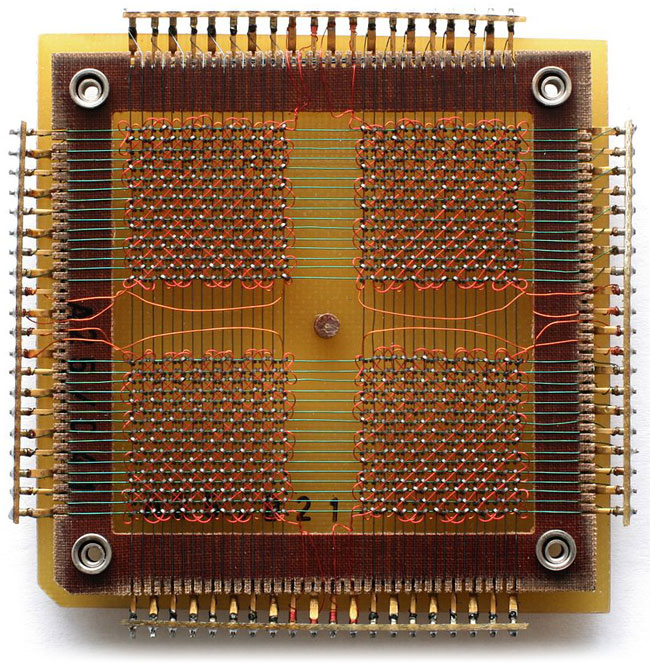

Les disques durs traditionnels se rangent dans la catégorie des mémoires non volatiles puisqu'ils sont capables de conserver leurs données en l’absence d'alimentation électrique. Mais pour nous autres puristes, une mémoire non volatile concerne avant tout les mémoires à accès direct, en d'autre terme la RAM. Une des toutes premières formes de mémoire RAM non volatile existant dans les années 1960 était d'ailleurs à base de tores de ferrite jusqu'au début des années 1970.

Mémoire non volatile datant de 1961 constituée de tores de ferrite pouvant stocker 1024 bits de données (c)Konstantin Lanzet

Une des technologies en vigueur à l'époque était la EAROM (Electrically Alterable Read Only Memory) dont la particularité était de perdre l'information au bout de quelques années d'usage. C'était un type d'EEPROM fonctionnant sur 12V qui ne pouvait modifier ses données qu'un seul bit à la fois, et dont le processus d'écriture était très long. En 1976, à partir de cette technologie, la société américaine Dataram a produit pour le constructeur DEC ce qui ressemble au tout premier disque de type SSD (sous la dénomination de Bulk Core) dont la capacité de stockage était de 2Mo.

Et pendant une quinzaine d'années, il y a eu une succession de concepts plus ou moins différents et novateurs, tels que la Bubble Memory d'Intel, les Romdisk d'IBM fabriqués par Curtis, ou encore les premiers lecteurs Adtron de carte mémoire fabriquées par Epson et Mitsubishi. Puis un jour de 1984, Toshiba a mis au point la mémoire NOR grâce aux travaux du Dr. Fujio Masuoka, et la mémoire NAND trois ans après, plus rapide et moins coûteuse à produire, qui se rependra largement les années suivantes à travers les mémoires Flash. Tout cela coïncide aussi avec le développement de l'intégration à très grande échelle des semi-conducteurs (VLSI) durant les années 1990 et 2000 dans lesquelles des circuits de plus en plus denses furent mis au point. Et entre 2007 et 2008, il fut envisagé d'exploiter ce genre de mémoire NAND dans un système de stockage de masse dans lequel elles sont organisées en matrice de 8 ou de 16 et pilotées par un contrôleur dédié : le concept du Solid-State Drive était posé.

Un des premiers disques SSD 2,5 pouces grand public SATA sorti en 2008, et oui on s'appelait encore Puissance PC !

On trouve beaucoup d'avantages au SSD par rapport à un disque dur traditionnel : pas de bruit, résistant aux chocs physiques, une consommation moindre, des temps d'accès aux données très largement inférieurs, et une latence beaucoup plus faible. Mais dès la sortie des premiers modèles, le prix était un facteur dissuasif, et encore aujourd'hui, bien que sur une pente descendante, le prix de l'octet NAND est toujours 4 à 7 fois supérieur à celui de l'octet magnétique.

Maintenant que le décor est planté, nous allons pouvoir nous intéresser de près à tous les aspects techniques d'un SSD et aborder sa conception, son architecture et ses composants.

Un SSD s'articule autour de 3 éléments fondamentaux : une série de mémoires NAND pour le stockage des données, une interface SATA pour relier le système à la carte mère de l'ordinateur, et un contrôleur central pour piloter le tout. Ajoutons à cela un quatrième élément qui est le module d'alimentation chargé, entre autre, de fournir aux composants les tensions précises nécessaires à leur fonctionnement, ainsi que la réserve d'une quantité de courant suffisante pour que le processeur ait toujours le temps de transférer les dernières données en cas de coupure de courant subite.

Nous verrons en détail ces 4 éléments dans la partie consacrée aux composants. On pourrait donc schématiser l'architecture d'un SSD par le diagramme suivant :

![3N C11QU4N7 C357 P1U5 6r4ND diagramme logique dun SSD [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/ssd_diag_t.png)

La logique simplifiée d'un lecteur SSD

Une série de mémoires NAND est répartie sur des canaux flash directement rattachés à un processeur dédié qui se charge de faire l'interface de communication entre l'ordinateur hôte et les mémoires qu'il contrôle. Il dispose d'une mémoire volatile DRAM pour l'aider à organiser son travail d'optimisation de la gestion des NAND. Aujourd'hui, l'interface de liaison la plus utilisée est le SATA, mais il existe aussi des SSD en FireWire ou en PCIexpress.

Le processeur en question est ce qu'on appelle dans le jargon électronique un ASIC (acronyme de Application Specific Integrated Circuit). C'est un microprocesseur complexe (semblable à un SoC), qui a été mis au point pour une tâche très spécifique. Il ne sait rien faire d'autre que ce pour quoi il a été conçu, mais par contre, il le fait bien et vite. Et entre autre, il est capable d'exécuter un grand nombre d'algorithmes compliqués qui vont lui permettre de prendre les meilleures décisions possibles en fonction des données qu'il doit relire, écrire, déplacer, supprimer ou réorganiser. Et parmi ces algorithmes, on trouve le code de correction d'erreur, la répartition de l'usure des NAND, la relocalisation des blocs de données, l'identification de mauvais blocs, le cache séquentiel en lecture et écriture, le recyclage de blocs mémoire préalablement alloués puis inutilisé, le chiffrement avancé en 128 ou 256 bits, ainsi que toutes les autres tâches essentielles mais plus spécifiques aux éléments périphériques. Ce contrôleur est vraiment la pièce maîtresse du système, et les performances globales du SSD ne dépendent essentiellement que de sa puissance de traitement. Un bon contrôleur est même en mesure de rendre robustes et fiables des mémoires NAND imparfaites.

Le schéma-bloc ci-dessous donne un aperçu de la façon dont il est généralement constitué.

![3N C11QU4N7 C357 P1U5 6r4ND diagramme logique dun contrôleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/ssd_diag_2_t.png)

En gros, comment pense le contrôleur de vos SSDs

Quelques explications sur le fonctionnement s'imposent. Tout d'abord, on remarque 2 parties distinctes : le « front-end » qui regroupe l'interface hôte SATA ainsi que le contrôleur SATA, et le « back-end » qui regroupe le traitement des commandes et des informations, ainsi que le système d'accès aux mémoires NAND, le tout connecté par un bus de données. Il est souvent préféré une configuration multi-processeurs. Dans ce schéma, FCPU indique le CPU du front-end et BCPU celui du back-end, et le travail se fait toujours en parallèle pour accélérer les vitesses d'exécution, d'où la nécessité d'exploiter des CPU multi-cœurs.

Dans la file, le module de gestion des commandes (Command queue), la technique du Native Command Queuing définie pour l'interface SATA est la plus adoptée dans ces contrôleurs pour des raisons de performance tout en permettant de recevoir des requêtes d'exécution non-séquentielles.

Le tampon de données (Data buffer) remplit la fonction d'adaptation de vitesse entre les accès depuis l'hôte et la mémoire NAND, et également d'écriture simultanée de multiples secteurs de données dans la mémoire NAND. La table de correspondance (LUT) détermine la relation entre l'adressage par bloc logique (LBA) et l'adresse physique dans la NAND.

Il faut noter qu'il n'est pas indispensable que les adresses en LBA et dans la NAND soient les mêmes, étant donné que le processeur tient à jour une carte de l'ensemble des adresses pour les parties logiques et physiques. Pour accéder à la table de gestion des adresses stockée dans la mémoire DRAM externe, l'ASIC dispose d'un mini-contrôleur interne DDR. Il dispose aussi d'un mini-contrôleur interne de NAND capable de prendre en charge le premier niveau de correction d'erreur ECC. Pour obtenir un niveau de bande passante optimal, les contrôleurs récents sont en mesure de gérer jusqu'à 8 canaux flash simultanément.

Concernant le cheminement des données en lecture et en écriture, un contrôleur suit généralement le mécanisme suivant :

![La magie de la loupe, sans loupe diagramme logique des données [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/ssd_diag_3_t.png)

Récapitulatif du chemin parcouru (en gris) par ces données en lecture ou en écriture depuis l'hôte

Abordons maintenant un disque SSD sous son aspect électronique pour en détailler ses composants. Étant donné que nous avons réalisé l'analyse qui suit en travaillant sur un modèle de chez OCZ, les observations seront donc parfois ciblées sur ce SSD. Mais pour ce qui nous intéresse là, le modèle ou la marque n'a aucune importance en soit car le mode opératoire est le même pour tous les SSD du marché.

![La magie de la loupe, sans loupe un banc de mesure au CDH [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/sonde_t.jpg)

Nous avions 2 oscilloscopes en simultané pour monitorer l'activité de ce SSD pendant l'analyse

Par contre, en conclusion de cet article, on passera en revue le circuit imprimé de quelques modèles connus afin de commenter les choix techniques voulus par leurs constructeurs.

Lorsqu'on observe le circuit imprimé d'un SSD, on peut distinguer 4 régions distinctes, toutes aussi essentielles les unes que les autres, au sein desquelles se trouvent des modules parfois constitués de plusieurs étages. On les identifie selon : CPU, NAND, Alimentation et Connecteurs.

![Cliquédélique ! le PCB dun SSD [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/pcb_explique_t.jpg)

PCB classique d'un SSD classique à base de SF-2281

Exclusivement constitué de composants de surface pour des raisons évidentes de densité d'intégration, ce type de circuit imprimé est de classe FR-4, c'est à dire qu'il est fait d'un composite de résine epoxy renforcé de fibre de verre. Il est multi-couche, et on ne doit pas être loin du compte en disant qu'il comporte au moins 2 couches conductrices internes en plus des 2 externes qui sont visibles sur la face avant et sur la face arrière. Un rapide coup d’œil sur le connecteur d'alimentation SATA nous permet d'affirmer que l'une des couches internes est d'ailleurs celle sur laquelle est distribuée la masse, car les broches de masse de ce connecteur rejoignent immédiatement des vias qui descendent vers une couche interne.

On remarquera aussi qu'il reste pas mal d'espace vide autour du processeur central et sur la seconde moitié de la face arrière. Le constructeur aurait donc pu miser sur un facteur de forme plus petit du circuit imprimé et augmenter ainsi le niveau d'intégration des composants.

Sur ces 2 faces externes recouvertes d'un vernis coloré, les pistes qui relient le contrôleur et les mémoires ne représentent qu'une petite partie du bus de données, le reste est enfoui dans les couches internes. C'est une technique de répartition courante, étant donné la largeur de ce bus par rapport à la petite surface à exploiter. On remarque également qu'il y a des cellules JTAG qui sont là pour nous permettre de monitorer l'activité des circuits intégrés auxquelles elles sont reliées, ou même d'intervenir dans leur système de commande.

![Cliquédélique ! PCB SSD : cellules JTAG [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/cellules_jtag_t.jpg)

Stoi le JTAG, bouffon (cliquez pour agrandir)

Et on trouve aussi sur cette carte un certain nombre de points de test nous permettant de mesurer les différents signaux qui les traversent afin de procéder à des vérifications de tension localisées ou à effectuer du debuging.

![Ne pas appuyer ici PCB SSD : points de tests [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/points_de_test_t.jpg)

Des chiffres et des lettres (cliquez pour ah ! grandir)

Présenté dans un boîtier BGA (soudé au circuit à partir d'une matrice de billes de soudure), et positionné de façon centrale sur le circuit pour être relativement équidistant des NAND, ce contrôleur dispose de son quartz électronique qui oscille à une fréquence de base (30.0 Mhz sur ce modèle OCZ), fréquence que le CPU va largement amplifier en interne pour atteindre des vitesses de cycle beaucoup plus importantes (de l'ordre d'au moins x10). Il faut également noter que ce quartz est aussi là pour fixer la fréquence d'horloge des mémoires NAND orchestrées par le contrôleur.

![Visionner en grand sur un magnifique pop-up PCB SSD : le contrôleur (ici un Sandforce 2281) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/sf2281_t.jpg)

Une puce pour les contrôleur toutes (cliquez pour agrandir)

Il faut savoir qu'à l'exception des quelques informations qu'ils acceptent de donner sur leurs plaquettes marketing, les fabricants ne communiquent que très rarement sur les détails techniques de leurs ASIC. Ils ne divulguent aucun datasheet ou schéma-bloc qui nous permettraient de faire les mesures pertinentes directement sur le composant pour mieux comprendre la nature du signal traité.

Par exemple, le diagramme ci-dessous extrait de la seule plaquette marketing du contrôleur SandForce SF-2281 de ce modèle OCZ, montre grossièrement les différents blocs de traitement ainsi que leur relation d'entrée/sortie au sein du processeur.

![Cliquédélique ! Sandforce 2281 I/O [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/diagram_bloc03_t.png)

Où est la zone rouge ? (cliquez pour agrandir)

Et mis à part le fait qu'il confirme que cette puce intègre bien un cache rapide interne (Buffer) que d'autres processeurs déportent dans une mémoire DRAM externe, nous n'apprenons hélas pas grand chose de pertinent.

Sur la face arrière du circuit imprimé, juste en dessous du contrôleur sont regroupés les condensateurs de découplage en céramique (ou parfois au tantale) dont le rôle est d'évacuer les harmoniques de haute et moyenne fréquence vers la masse afin de nettoyer tous les parasites susceptibles de perturber son bon fonctionnement.

![3N C11QU4N7 C357 P1U5 6r4ND SSD PCB : nettoyage électriques du contrôleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/condecoup_t.jpg)

On ne voit pas très bien (quoique, cliquez pour agrandir) mais il y'a plein de micro-conchitas qui nettoient le signal

Et pour une efficacité optimale, la distance entre eux et les broches du circuit intégré doit être la plus courte possible, d'où leur présence juste en-dessous du boîtier. Ils n'ont alors que les couches internes de la carte mère à traverser.

Le contrôleur est un microprocesseur dédié, et il est fréquent que les ingénieurs adoptent désormais une architecture multi-coeur basée ARM 32 bits, en y intégrant une circuiterie propriétaire pour les blocs-modules d’interfaçage avec les mémoires, le cache et le SATA. Et comme tout microprocesseur, il exécute un code machine. Pour le grand public, ce code est connu sous l'appellation « Firmware ». Lorsqu'on fait une mise à jour de ce firmware à partir d'un système d'exploitation quelconque (Windows, MacOSX, Linux ou autre), le nouveau code est réinjecté dans l'EEPROM interne du contrôleur à la place de l'ancien. Ensuite, il se place dans un état de réinitialisation logicielle pour recharger et exécuter le nouveau firmware, le tout ne prenant que quelques centaines de millisecondes.

Sur son circuit imprimé, ce modèle OCZ ne présente pas de mémoire volatile DRAM en guise de cache car son contrôleur SandForce en dispose déjà en interne. Mais il est assez fréquent qu'un contrôleur se fasse épauler par un composant DDR DRAM dont les temps d'accès se mesurent en nanosecondes. A partir d'algorithmes intelligents, l'usage d'un cache en mémoire dynamique permet au processeur de réorganiser des écritures de données aléatoires de taille variable en blocs séquentiels et de les transférer alors aux NAND sous cette nouvelle forme. On obtient ainsi une écriture faiblement amplifiée et parfaitement optimisée : usage de blocs importants sur de grandes pages et niveau de latence le plus faible possible.

Ce type de mémoire est très souvent présenté dans un boîtier TSOP 48 broches (avec 24 broches de part et d'autre de la puce) bien qu'on en voit apparaître de plus en plus dans un facteur de forme BGA (notamment chez Samsung et Toshiba).

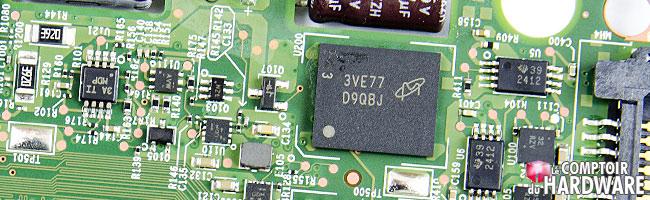

![Visionner en grand sur un magnifique pop-up mémoires NAND [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/nand_t.jpg)

Des puces NAND Micron 25nm asynchrones (cliquez, agrandir, tout ça)

Actuellement, la plus petite finesse de gravure qui est utilisée pour concevoir ces mémoires est de 15nm (soit 15x10-9 mètre !). Pour que les choses soient bien claires, cette valeur correspond au diamètre du plus petit connecteur reliant deux composantes du circuit intégré. A titre de comparaison, c'est environ 8000 fois plus petit qu'un cheveux d'adulte humain.

Il a été possible de déterminer que le diamètre d'un atome de silicium était de 0,1nm, ce qui sous entend que, dans un futur proche, lorsque la finesse de gravure en vigueur sera de l'ordre de 10nm, le connecteur en question aura un diamètre équivalent à un alignement de 100 atomes de silicium, ce qui est tout simplement incroyable. Et il arrivera alors un point où le nombre d'atome sera tellement bas que le comportement électrique qui en résultera relèvera plus de la physique quantique que de la physique classique. Ce sera alors probablement une nouvelle ère technologique qui s'ouvrira à nous. Et bien entendu, obtenir des mémoires avec des finesses de gravure toujours plus basses a pas mal d'avantages, notamment une consommation électrique moindre pour une densité de stockage plus importante et un coût de fabrication plus faible une fois que la technique est maîtrisée.

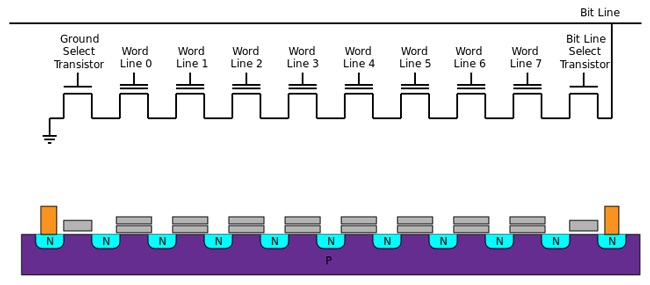

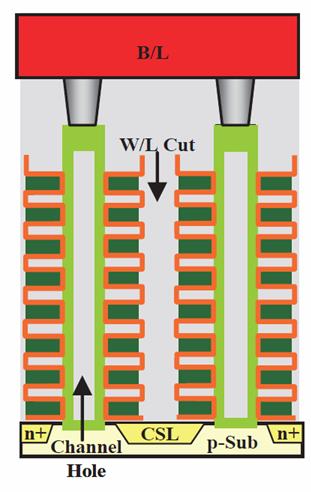

La structure planaire de base d'une NAND

A l'instar d'une EEPROM, la structure électronique d'une mémoire NAND repose sur un alignement planaire de transistors à effet de champ à grille métal-oxyde (MOSFET) possédants une grille flottante enfouie au milieu de l'oxyde de grille. Et pour que l'information soit stockée, on va chercher à piéger les électrons dans cette grille flottante en leur faisant traverser l'oxyde. Et pour cela, le méthode la plus fréquemment employée est le fameux effet tunnel, qui est un effet purement quantique assez complexe à décrire, qui s'obtient en appliquant une haute tension sur la grille de contrôle.

![Ne pas appuyer ici Leffet tunnel [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/nand_fg_t.png)

La grille isolée constitue un excellent piège à électrons permettant de garantir la rétention de charge pendant plusieurs dizaines années consécutives. Ce mécanisme de stockage de base s'appelle une cellule, et une mémoire NAND en contient quelques milliards, chacune pouvant stocker de 1 à 3 bits de données selon le type de mémoire produite. Concernant la NAND flash, il en existe de trois sortes :

Pour écrire ou effacer une donnée, on applique différentes tensions aux points d'entrée de la cellule. Et contrairement à la lecture qui n'a aucune incidence sur l'usure de la grille flottante, l'écriture d'une information a pour effet secondaire de l'user progressivement. C'est la raison qui fait que ce type de mémoire a une durée de vie déterminée. En effet, il a été observé qu'une cellule de type SLC a une durée de vie de 100 000 cycles d'écriture/effacement. Et c'est là qu'interviennent les algorithmes de répartition de l'usure des cellules pour diminuer cet inconvénient (connus sous l'appellation Wear Leveling), mais ce traitement additionnel peut potentiellement provoquer certains ralentissements en écriture dus aux relocalisations successives des blocs de données.

Un assez gros inconvénient de la mémoire NAND par rapport à la mémoire NOR, est que la NAND a besoin d'un code correcteur d'erreur (ECC) pour assurer l'intégrité du stockage des bits de données. C'est la raison pour laquelle, une NAND contient des plages de stockage supplémentaire sur chaque page pour y stocker le code de correction, ainsi que d'autres données utilisées par le contrôleur au niveau de la répartition de l'usure, de la logique liée à la relocalisation de blocs, etc. En général, la taille de cet espace supplémentaire est de 16 octets par secteur de 512, bien qu'il arrive que les fabricants modifient parfois ce rapport en fonction du nombre de cellules contenus dans les matrices de transistors.

Il y a environ 5 ans, il a été émis l'idée de structurer ces cellules de façon à exploiter une organisation à la fois verticale et horizontale (3D) plutôt qu'en alignement planaire (2D) comme c'est le cas aujourd'hui. Et depuis, quelques gros fabricants travaillent d'arrache-pied sur ce concept novateur avec pour objectif d'entrer en production de masse dès que possible. Et avec sa nouvelle technologie V-NAND (le V symbolise la notion de verticalité), Samsung a tiré le premier en l'intégrant dans son modèle de SSD haut de gamme 850PRO, et ils annoncent déjà pouvoir fournir un SSD de 8To d'ici 2017 grâce à cette technologie.

L'innovation se place au niveau de la façon de retenir la charge électrique dans une cellule. Au lieu d'utiliser une grille flottante planaire MOSFET, Samsung utiliserait du nitrure de silicium (formule brute Si3N4) non-conducteur en couche, ce qui leur permettrait de palier les interférences entre cellules, et de pouvoir ainsi les empiler les unes sur les autres jusqu'à une hauteur de 32.

Paradoxalement, cette technique de piège à électrons utilisant du nitrure de silicium appelée « Charge Trap Flash » (CTF) a été initialement mise au point au début des années 2000 par AMD en collaboration avec Fujitsu pour créer une autre forme de mémoires NOR et NAND beaucoup moins coûteuses à produire.

Dans la mesure où chaque modèle différent de SSD dispose de son propre module d'alimentation adapté à l'architecture en place, il nous sera difficile cette fois de rester généraliste dans nos propos. C'est pourquoi on sera un peu plus spécifique au modèle OCZ dont nous disposons puisque les étages d'alimentation que l'on voit sur les photos ci-après sont ceux visibles sur son circuit imprimé. Cependant, toutes ces alimentations pour SSD ont les mêmes objectifs que l'on pourrait résumer en trois points :

Tout module d'alimentation qui ne respecterait pas tous ces points ne permettrait malheureusement pas au SSD d'être aussi efficace et irréprochable que les autres.

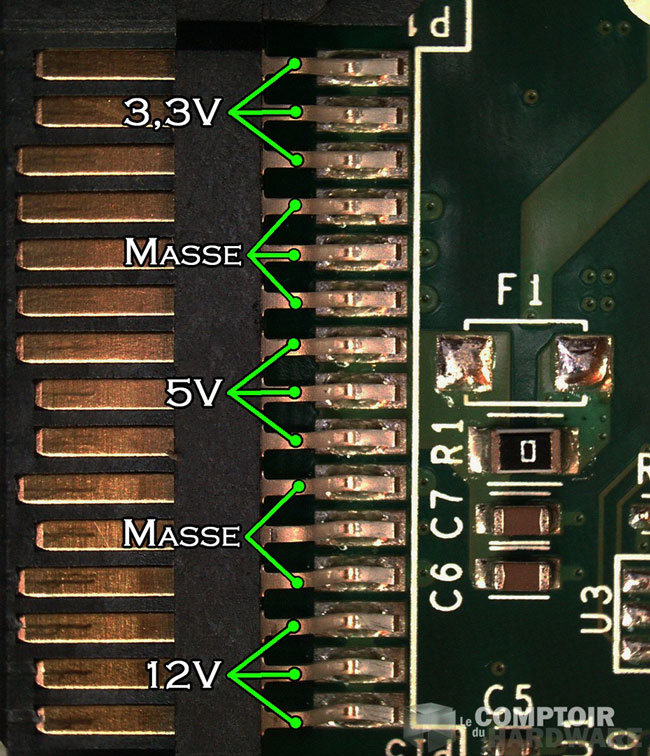

La broche d'alimentation SATA fournit les 3 tensions traditionnelles +3.3V, +5V et +12V, mais un SSD n'utilise que le +5V plus la masse.

Les broches électriques du connecteur SATA

On voit d'ailleurs très bien sur cette image que les broches 7,8,9 sont toutes reliées à la même piste +5V, et que les broches 4,5,6,10,12 rejoignent la couche interne de masse par leurs vias. A cette entrée de tension +5V, il y a 3 composants de surface soudés en parallèle, 2 condensateurs (C6 & C7) et une résistance 0 ohm (R1) qui joue ici le rôle de shunt. L'emplacement F1 devrait normalement recevoir un fusible SMD, mais il n'est pas peuplé, et c'est plutôt à travers ce pont à faible impédance R1 que le courant passera. Choix discutable nous diriez-vous ? Ça dépend. Il est vrai qu'à des niveaux de consommation de courant aussi faible (les SSD ne drainent rarement plus de 400 mA en accès), le risque est calculé.

Le principal composant du premier étage de régulation est ce boîtier SO-8 à double MOSFET de puissance à canal-N.

![Visionner en grand sur un magnifique pop-up le 1er étage de régulation électrique [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/irf9910_t.jpg)

Un MOSFET irf9910 pour réguler la tension en entrée de signal (vous pouvez même agrandir)

Il est utilisé ici comme régulateur de tension à partir d'un circuit de filtrage RC (résistance+condensateur) et il a la particularité de pouvoir le faire pour deux tensions simultanées. Et nous avons pu mesurer que les tensions qu'il délivre à ses bornes D1 et D2 sont respectivement de 2,852V et 1,039V, on est donc dans une plage de tension faible.

Et on remarque sur le circuit imprimé que ses bornes de désignation D1 et D2 sont les entrées de 2 modules identiques mais séparés, composés chacun de 3 gros condensateurs au tantale et d'un imposant boîtier QFN de 38 broches qui n'est autre qu'un PowerSoC spécialisé dans l'alimentation de précision des microprocesseurs multi-cœur basse consommation, comme c'est en l’occurrence le cas des contrôleurs de SSD.

![3N C11QU4N7 C357 P1U5 6r4ND lalimentation du contrôleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/en6337_t.jpg)

L'alimentation du contrôleur (cliquez pour y voir en graaaaand)

A lui tout seul, il est une sorte de micro-alimentation à découpage, et intègre même une solénoïde. Il joue ici le rôle de convertisseur de courant continu à pulsation (qu'on appelle aussi convertisseur continu-continu, convertisseur Buck), c'est à dire qu'il assure la fluence d'énergie entre une source de tension continue et une source de courant continu.

![Cliquédélique ! diragrame logique dun powerSOC EN6337 [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/en6337_diag_t.png)

Le diag logique du PowerSOC EN6337 (que même vous pouvez aagrandir grâce à la magie du clic)

La raison pour laquelle il y a 2 modules identiques en tout point est parce que nous avons à faire à un étage d'alimentation redondante. Les modules sont disposés en parallèle avec une commutation dynamique commandée par un transistor afin que le module auxiliaire s'active si un problème de tension intervient au niveau du module principal. Le principe d'alimentation redondante est une pratique devenue courante pour un SSD pour jouer la carte de la fiabilité.

Concernant le choix des condensateurs au tantale à faible résistance équivalente, ils sont parfaitement dimensionnés pour fournir la capacité nécessaire au processeur pour flusher les données en cours de traitement avant de s'éteindre proprement après une coupure d'alimentation.

![Ne pas appuyer ici condensateurs au tantale [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/condensateurs_t.jpg)

![Visionner en grand sur un magnifique pop-up condensateurs au tantale [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/watchdog_t.jpg)

Les condos au tantale à gauche, le watchdog à droite (cliquez pour voir la vie en plus grand)

Mais le système ne serait pas complet s'il ne disposait pas d'un « chien de garde », et c'est justement le rôle de ce circuit intégré programmable PWR607 à 32 broches QFNS.

Il supervise l'activité de tous les étages d'alimentation du circuit et est capable de provoquer une réinitialisation système si une action prédéfinie n'est pas exécutée dans un délai imparti, ce qui sous-entendrait l'existence d'un problème potentiel. Ce type de protection est gage de qualité dans un module d'alimentation de ce type.

![Visionner en grand sur un magnifique pop-up superviseur PWR607 [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/csm/powr607_diag_t.png)

A gauche, le schéma de principe en application – A droite, le schéma-bloc interne du composant (cliqouillez pour agrandissage)

A l'instar d'un FPGA qui doit charger sa configuration depuis une mémoire non volatile pour être opérationnel, ce chien de garde conçu autour d'un PLD de 16 macro-cellules charge son code depuis une EEPROM. Dans le cas de notre modèle OCZ, l'EEPROM en question est un composant basse tension de 256Koctets en boîtier 8 broches TSSOP placé juste à ses cotés. L'interface JTAG à 5 broches libellée J3 lui est d'ailleurs également dédiée.

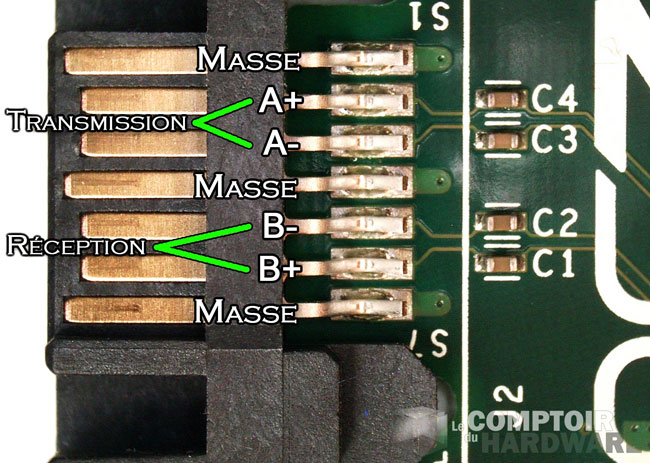

Au niveau du câble de données du connecteur SATA, les informations sont transmises par 2 paires différentielles (une paire pour la transmission et une pour la réception) protégées par 3 fils de masse. Le standard SATA utilise une ligne symétrique pour diminuer l'influence des perturbations électromagnétiques. On voit que les 4 pistes sont directes vers le contrôleur en traversant des passifs C1 à C4, classique, sans grande surprise...

Les broches data du connecteur SATA

Nous avons donc terminé notre analyse de composant en essayant de rester le plus généraliste possible. Passons maintenant en revue quelques circuits imprimés de modèles de SSD connus afin de commenter les choix techniques des fabricants.

En conclusion de cet article, attardons nous quelque peu sur un certain nombre de circuits imprimés de modèles relativement récents de SSD 2,5 pouces afin de faire quelques observations sur les choix et les architectures mises en place par les constructeurs. Sur un plan strictement électronique, il y a des critères qui nous semblent important à considérer, tels quel le design du circuit, le degré de réparation ou encore la robustesse de l'alimentation. En d'autres termes, il s'agit de pouvoir juger de la cohérence de l'agencement des composants et de l'optimisation du tracé des pistes, de savoir si en cas de panne le circuit est adapté à une session de dépannage par un électronicien, ou encore de connaître le type de design d'alimentation à découpage et son potentiel de fiabilité.

Et bien entendu, ces observations découlent de nos analyses des circuits imprimés et non pas de ce que l'on pourrait éventuellement lire dans d'autres articles sur ces modèles. Par ailleurs, il serait logique qu'un modèle qui introduise la terminaison « Pro » dans son intitulé puisse être utilisé en entreprise, dans des machines qui font du stockage intensif, ou même encore dans des serveurs. Cela sous-entend donc que le module d'alimentation dont il dispose soit irréprochable en terme de robustesse, de stabilité, de protection, et de redondance puisque c'est lui qui gère le courant nécessaire à tous les circuits intégrés du système. Et bien vous risquez d'avoir quelques surprises...

![Enlarge your pe...icture seagate 600 dessus (il aime dominer le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/seagate/600-240/seagate_600-av_t.jpg)

![Si vous cliquez, vous cliquez. seagate 600 derrière (il aime être dominé le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/seagate/600-240/seagate_600-ar_t.jpg)

![La magie de la loupe, sans loupe seagate 600 pcb conntrolleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/seagate/600-240/seagate_600-av_pcb_t.jpg)

![Cliquédélique ! seagate 600 pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/seagate/600-240/seagate_600-ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Le design de ce PCB bâti sur un contrôlleur LAMD est particulièrement propre et optimisé. La couche supérieure externe est celle dédiée à l'alimentation des composants de surface, et toutes les autres couches internes définissent le bus de données. Et comme à leur habitude, Seagate à cherché à garder la face arrière vierge de tout composant ou vias. Du grand art de multi-layering.

L'agencement des circuits intégrés (tous en boîtier BGA) est aussi parfaitement équilibré autour du contrôleur Link-A-Media LM87800. On fait aussi usage d'un tracé de pistes sinueuses pour contrôler l'impédance pour la synchronisation du routage du signal. Par contre, le manque de points de test et l'absence de labellisation des composants sur le circuit est la preuve que ce SSD n'est pas du tout prévu pour un dépannage.

Ce modèle dispose d'une alimentation à découpage relativement classique, avec 4 régulateurs de tension continue faible perte dont 2 pour la redondance du dernier étage. La protection installée est basique, essentiellement assurée par des diodes de puissance. Ce module d'alimentation a un travail a faire, et il le fait correctement, mais sans aucune supervision ni surveillance de la part d'un circuit intégré spécialisé. Il faut savoir que Seagate a également sorti la version 600 Pro, résolument tourné vers un usage en entreprise. Autant le module d'alim du 600 est plutôt classique, autant celui du 600 Pro est sérieusement blindé avec une redondance à tous ses étages, un chien de garde et des condensateurs de backup surdimensionnés. Mais c'est la seule réelle différence notable entre les deux modèles.

![Ne pas appuyer ici corsair force 3 gt dessus (il aime dominer le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/corsair/force3gt-120/force3gt-120_av_t.jpg)

![La magie de la loupe, sans loupe corsair force 3 gt derrière (il aime être dominé le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/corsair/force3gt-120/force3gt-120_ar_t.jpg)

![Si vous cliquez, vous cliquez. corsair force 3 gt pcb conntroleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/corsair/force3gt-120/force3gt-120_av_pcb_t.jpg)

![Si vous cliquez, vous cliquez. corsair force 3 gt pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/corsair/force3gt-120/force3gt-120_ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Même s'il fait partie d'une ancienne génération, nous avons trouvé intéressant de se pencher sur ce modèle. Le PCB a été dessiné pour que le module d'alimentation ne se retrouve essentiellement que sur la face arrière, ce qui est plutôt une bonne idée. La face avant regroupe ainsi le contrôleur LSI Sandforce SF2281 accompagné de son quartz et de la première moitié des NAND Micron, le reste est bien entendu sur la face arrière, en parfaite symétrie. De la façon dont ils sont alignés, on sent une réelle volonté d'organisation méticuleuse des résistances et condensateurs par rapport aux circuits intégrés qu'ils connectent.

Ça permet non seulement d'optimiser l'agencement des éléments, mais ça facilite aussi le dépannage. Et à ce propos, ce circuit imprimé fourmille de libellés qui renseignent la nature des composants, ainsi que d'une quarantaine de points de tests disposés à proximité des zones sensibles. On ne demande pas mieux pour pouvoir le réparer. Le module d'alimentation dispose de 2 chiens de garde parallèles, un par canal flash et d'un système de régulation de tension assuré par des régulateurs de tension faible perte faible consommation. Le courant semble parfaitement maintenu, stocké et dénué de hautes fréquences parasites d'un bout à l'autre de la chaîne.

![Enlarge your pe...icture crucial MX100 dessus (il aime dominer le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/crucial/mx100-512/crucial-mx100-av_t.jpg)

![Visionner en grand sur un magnifique pop-up crucial MX100 derrière (il aime être dominé le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/crucial/mx100-512/crucial-mx100-ar_t.jpg)

![Ne pas appuyer ici crucial MX100 pcb conntrolleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/crucial/mx100-512/crucial-mx100-av_pcb_t.jpg)

![Même pas cap' de cliquer crucial MX100 pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/crucial/mx100-512/crucial-mx100-ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Ce qui saute immédiatement aux yeux lorsqu'on observe la face avant de ce PCB à base Marvell, c'est le choix de l'agencement des composants passifs dédiés aux 16 mémoires NAND. Dans un soucis de faciliter le debugging, les condensateurs au tantale et les résistances sont tous alignés en rang d'oignon, ou regroupés en blocs de 2x4 résistances donnant accès à tous leurs points de test. Et à propos de points de test, il y en a partout disséminés sur le circuit. Absolument tous les composants peuvent être monitorés sur un oscilloscope, y compris le contrôleur Marvell 88SS9189... Le paradis pour un électronicien !

Par contre, il n'y a aucune labellisation des composants. On remarque aussi que les ingénieurs ont choisi de ne faire remonter à la surface qu'une petite quantité de pistes et d'opter plutôt pour le multi-layering intensif, probablement sur 5 ou 6 couches. Le module d'alimentation à découpage est assez impressionnant dans son design. Là encore, il a été découpé et répartit sur le circuit selon les étages. Le contrôleur dispose de son propre étage de régulation, ainsi que les NAND, le tout sous le contrôle d'un système de supervision assuré par un microcontroleur MSP430, ce qui en fait un des SSD les mieux équipés pour palier à tout problème électrique potentiel. Pour un positionnement d'entrée de gamme qui aura clairement boulversé le marché en 2014, Crucial n'a pas fait les choses à moitié !

En conclusion de cet article, attardons nous quelque peu sur un certain nombre de circuits imprimés de modèles relativement récents de SSD 2,5 pouces afin de faire quelques observations sur les choix et les architectures mises en place par les constructeurs. Sur un plan strictement électronique, il y a des critères qui nous semblent important à considérer, tels quel le design du circuit, le degré de réparation ou encore la robustesse de l'alimentation. En d'autres termes, il s'agit de pouvoir juger de la cohérence de l'agencement des composants et de l'optimisation du tracé des pistes, de savoir si en cas de panne le circuit est adapté à une session de dépannage par un électronicien, ou encore de connaître le type de design d'alimentation à découpage et son potentiel de fiabilité.

Et bien entendu, ces observations découlent de nos analyses des circuits imprimés et non pas de ce que l'on pourrait éventuellement lire dans d'autres articles sur ces modèles. Par ailleurs, il serait logique qu'un modèle qui introduise la terminaison « Pro » dans son intitulé puisse être utilisé en entreprise, dans des machines qui font du stockage intensif, ou même encore dans des serveurs. Cela sous-entend donc que le module d'alimentation dont il dispose soit irréprochable en terme de robustesse, de stabilité, de protection, et de redondance puisque c'est lui qui gère le courant nécessaire à tous les circuits intégrés du système. Et bien vous risquez d'avoir quelques surprises...

![Enlarge your pe...icture intel 730 dessus (il aime dominer le coquinou) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/intel/730-480/intel-730-av_t.jpg)

![Visionner en grand sur un magnifique pop-up Intel 730 derrière (cest plus discret) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/intel/730-480/intel-730-ar_t.jpg)

![Ultra bouzotron HD max def Intel 730 pcb conntroleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/intel/730-480/intel-730-av_pcb_t.jpg)

![La magie de la loupe, sans loupe intel 730 pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/intel/730-480/intel-730-ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Quand un constructeur fait le choix de concevoir 90% des composants d'un SSD comme c'est le cas ici pour Intel, on se doute que le résultat sera à la hauteur. Et en effet, ce SSD est techniquement irréprochable, ce qui donne un modèle robuste résolument tourné vers les pros et les entreprises.

Le design du circuit reste classique et ne doit pas comporter beaucoup de couches internes au vu de la densité du tracé des pistes externes sur les faces avant et arrière, mais le degré d'intégration des composants est assez important. Points de test en quantité suffisante, labellisation de tous les composants, cellule JTAG, tout est là pour nous permettre de monitorer, debugger et donc dépanner si besoin dans de bonnes conditions.

Ce modèle bénéficie d'un travail de conception de son module d'alimentation à découpage tout à fait remarquable qui surclasse ses concurrents et lui confère une robustesse et une efficacité redoutable. En effet, tous les étages sont redondants et les nombreuses phases délicates de conversion continu-continu sont assurées par une armée de régulateurs de tension de précision MOSFET ainsi que d'une chaîne de filtrage du courant qui lui retire les harmoniques indésirables pour qu'il soit le plus pur possible pour le contrôleur et ses mémoires. Intel a même choisi d'utiliser 2 condensateurs électrochimiques de 47uF en 35V (redondance oblige) pour assurer la quantité d'énergie nécessaire pour que le contrôleur puisse terminer correctement une tâche cruciale en cas de coupure de courant. Quand il s'agit de faire un design électronique de haut vol, Intel est un sérieux concurrent.

![Si vous cliquez, vous cliquez. OCZ octane dessus (il aime dominer le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/ocz/octane_128/octane-128_av_t.jpg)

![Ne pas appuyer ici OCZ octane derrière (il aime être dominé le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/ocz/octane_128/octane-128_ar_t.jpg)

![Enlarge your pe...icture OCZ octane gt pcb conntrlleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/ocz/octane_128/octane-128_av_pcb_t.jpg)

![Ultra bouzotron HD max def OCZ octane pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/ocz/octane_128/octane-128_ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Ce modèle était sorti en 2011 et ne s'est pas avéré être une grande réussite pour la firme Américaine, avec notamment des problèmes assez récurrents de fiabilité. Et quand on regarde son circuit imprimé à base Indilinx, on peut en effet se demander si OCZ n'a pas plutôt mis sur le marché un prototype de SSD, tellement son design nous donne parfois l'impression d'être encore en cours d'élaboration.

Visuellement, il y a déjà 3 points techniques qui nous semblent très discutable, notamment la disposition asymétriques des mémoires NAND Intel, la quantité démesurée de points de test associés aux NAND (8 par mémoire, soit 128 au total) qui sont en plus disposés un peu n'importe comment sur la face avant, et la large portion de circuit sur la face arrière dénué de tout composant qui trahit un manque d'optimisation du layout.

Difficile d'obtenir quelque chose d'irréprochable avec tout ça. De plus, on pourrait ajouter à cela le fait que 15 réseaux de résistances sont manquants (8 sur la face avant et 7 sur la face arrière) et que la protection primaire est assurée par une diode vraisemblablement sous-dimensionnée. Cela étant, le module d'alimentation est plutôt bien pensé, et fait bon usage d'un PowerSoC EN6337 parfaitement adapté à l'alimentation de microprocesseurs multi-cœur basse consommation comme c'est le cas du contrôleur Indilinx qu'il embarque. Mais ils n'ont pas opté pour la redondance à cet étage. Qu'à cela ne tienne, tout le système est sous la surveillance d'un chien de garde programmable Lattice POWR605 de 16 macrocellules, et c'est assurément un vrai plus technologique, à condition qu'il n'y ait pas de fail dans le code logique stocké dans l'EEPROM par OCZ, sinon le système ne sera pas sans faille. En bref, ce SSD est sans doute sorti trop tôt de leur laboratoire, et ils n'ont pas eu d'autre choix que de revoir leur copie au modèle suivant qui, en effet, s'est avéré être beaucoup moins perfectible et mieux conçu.

![La magie de la loupe, sans loupe OCZ vector dessus (pas de soumission) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/ocz/vector_256/ocz-vector-av_t.jpg)

![Ultra bouzotron HD max def OCZ vector derrière (soumi un peu, quand même) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/ocz/vector_256/ocz-vector-ar_t.jpg)

![Si vous cliquez, vous cliquez. OCZ vector pcb conntrolleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/ocz/vector_256/ocz-vector-av_pcb_t.jpg)

![La magie de la loupe, sans loupe OCZ vector pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/ocz/vector_256/ocz-vector-ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Malgré des soucis de fiabilité sur certains de leurs précédents modèles tel que l'Octane revu plus haut, OCZ sait produire des circuits imprimés au design soigné et suffisamment ouvert pour le debugging. Ça se vérifie sur ce modèle Vector, toujours sur base Indilinx (logique puisqu'ils ont racheté la marque et ses brevets) mais ils ont remplacé cette fois les points de test par une interface propriétaire à 52 connecteurs visible sur le côté opposé au connecteur SATA.

Autour du contrôleur central Indilinx Barefoot BF3 sont disposées les 16 mémoires NAND de façon symétrique par rapport aux 2 faces du circuit. L'armée de composants passifs (résistances + condensateurs en céramique) est confortablement installée à proximité des circuits intégrés qu'elle filtre et protège. Mais ce qui nous a un peu déconcerté, c'est la relative simplicité du design du module d'alimentation installé, conçu autour d'un triple convertisseur Buck synchrone MOSFET TPS652510 de chez Texas Instruments, assisté de quelques transistors de puissance, et c'est tout...

Certes, c'est une belle bête de management d'alimentation pour circuits intégrés complexes, incluant, entre autre, un système complet de supervision dit « chien de garde », mais OCZ a délibérément choisi de s'en remettre à lui sans prévoir de système auxiliaire ni de redondance dans le cas où le module principal deviendrait défaillant ou surchargé. Serait-ce pour limiter les coûts de fabrication ?

En conclusion de cet article, attardons nous quelque peu sur un certain nombre de circuits imprimés de modèles relativement récents de SSD 2,5 pouces afin de faire quelques observations sur les choix et les architectures mises en place par les constructeurs. Sur un plan strictement électronique, il y a des critères qui nous semblent important à considérer, tels quel le design du circuit, le degré de réparation ou encore la robustesse de l'alimentation. En d'autres termes, il s'agit de pouvoir juger de la cohérence de l'agencement des composants et de l'optimisation du tracé des pistes, de savoir si en cas de panne le circuit est adapté à une session de dépannage par un électronicien, ou encore de connaître le type de design d'alimentation à découpage et son potentiel de fiabilité.

Et bien entendu, ces observations découlent de nos analyses des circuits imprimés et non pas de ce que l'on pourrait éventuellement lire dans d'autres articles sur ces modèles. Par ailleurs, il serait logique qu'un modèle qui introduise la terminaison « Pro » dans son intitulé puisse être utilisé en entreprise, dans des machines qui font du stockage intensif, ou même encore dans des serveurs. Cela sous-entend donc que le module d'alimentation dont il dispose soit irréprochable en terme de robustesse, de stabilité, de protection, et de redondance puisque c'est lui qui gère le courant nécessaire à tous les circuits intégrés du système. Et bien vous risquez d'avoir quelques surprises...

![Cliquédélique ! plextor M5P dessus (comme un dominator) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/plextor/m5p-512/plextor-m5p-av_t.jpg)

![Ultra bouzotron HD max def plextor M5P derrière (et pan) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/plextor/m5p-512/plextor-m5p-ar_t.jpg)

![Visionner en grand sur un magnifique pop-up plextor M5P pcb conntrolleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/plextor/m5p-512/plextor-m5p-av_pcb_t.jpg)

![La magie de la loupe, sans loupe plextor M5P gt pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/plextor/m5p-512/plextor-m5p-ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Pas de grande originalité dans le design de ce circuit à base de Marvell, très répandue sur le marché. NAND symétriques horizontalement et verticalement, y compris au niveau de leurs composants passifs, disposition verticale du bloc processeur DRAM / Contrôleur / EEPROM / Quartz, alimentation à découpage installée en double face, et interface JTAG 10 points pour le debugging.

Un gros effort de labellisation des composants a cependant été fourni, ce qui n'est pas un mal. Mais on arrive rapidement à ce qui est à nos yeux le point faible de ce modèle, son alimentation, avec une conception très classique, limite basique pour un SSD. Un seul étage de régulation assurée par 2 régulateurs et un convertisseur Buck, aucune redondance sur système auxiliaire, et bien entendu, aucune supervision d'activité.

Cela étant, le courant traverse un bon mécanisme de filtrage comportant une large panoplie de condensateurs au tantale, et le stockage du courant semble être assuré pour palier au manque de tension subit. Mais, on a clairement vu mieux en la matière.

![Même pas cap' de cliquer plextor m6e dessus (il aime dominer le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/plextor/m6e-256/plextor-m6e-av_pcb_t.jpg)

![Ne pas appuyer ici plextor m6e derrière (il aime être dominé le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/plextor/m6e-256/plextor-m6e-ar_pcb_t.jpg)

A oilp (cliquez pour agrandir)

Ce modèle hybride à base de controlleur Marvell, est au facteur de forme M.2 et s'insère dans une carte fille PCI express. Pour un SSD en PCIexpress qui ne consomme pas plus de 400mA, la robustesse de l'alimentation est également moins sollicitée car le courant qui circule dans ce type de bus est en principe déjà supervisé et correctement régulé.

C'est la raison pour laquelle ce SSD ne dispose que d'un étage de régulation locale et conversion de courant continu à pulsation pour les circuits intégrés qu'il emploie. Un minimum de stockage et de filtrage est cependant effectué pour protéger le système contre une panne subite. Mais le moins que l'on puisse dire, c'est que Plextor a cherché à obtenir un niveau d'intégration sans faille avec un minimum de composants. Par contre, pour ce qui est de pouvoir le debugger, on repassera...

![La magie de la loupe, sans loupe samsung 850 pro dessus (il aime montrer son carré rouge) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/samsung/850pro-512/samsung-850po-av_t.jpg)

![Même pas cap' de cliquer samsung 850 pro derrière (il aime aussi le cacher) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/samsung/850pro-512/samsung-850po-ar_t.jpg)

![Ultra bouzotron HD max def samsung 850 pro pcb conntrolleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/samsung/850pro-512/samsung-850po-av_pcb_t.jpg)

![Ultra bouzotron HD max def samsung 850 pro pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/samsung/850pro-512/samsung-850po-ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Ce modèle exploitant la technologie de mémoire V-NAND en 3D et forcément basé sur le controleur MEX représente à ce jour le haut de gamme du constructeur coréen. Est ce que cela se ressent dans la conception de ses entrailles ? Dans l'absolu, oui, mais la réponse n'est pas aussi évidente quand on le compare au 840 Pro qui faisait déjà preuve d'un design à la fois soigné et efficace. Samsung a cette fois opté pour une conception épurée, utilisant beaucoup moins de composants passifs tout en gardant le circuit fortement multicouche.

Mais du coup, on se retrouve avec un agencement très clairsemé. Et ça n'est pas pour autant qu'ils en ont profité pour y placer des points de test ou une interface JTAG, il en est absolument dénué. Autour du couple processeur ARM + mémoire DRAM sont disposées les 4 mémoires NAND sur chaque face, le reste a un rapport direct ou indirect avec l'alimentation. Bien qu'il nous ait été impossible de l'identifier avec précision, un circuit intégré en boîtier QFP de 36 broches aurait la charge du management et de la supervision de l'alimentation à découpage. La conversion continu-continu multiple est assurée par des régulateurs faible perte MOSFET, mais nous n'avons détecté aucune redondance du système, ce qui est assez troublant si on considère utiliser ce type de SSD dans des machines très sollicitées comme le suggère sa démoniation "pro". Ce n'est donc pas un design qui nous aura impressionné, contrairement à celui de l'Intel 730.

En conclusion de cet article, attardons nous quelque peu sur un certain nombre de circuits imprimés de modèles relativement récents de SSD 2,5 pouces afin de faire quelques observations sur les choix et les architectures mises en place par les constructeurs. Sur un plan strictement électronique, il y a des critères qui nous semblent important à considérer, tels quel le design du circuit, le degré de réparation ou encore la robustesse de l'alimentation. En d'autres termes, il s'agit de pouvoir juger de la cohérence de l'agencement des composants et de l'optimisation du tracé des pistes, de savoir si en cas de panne le circuit est adapté à une session de dépannage par un électronicien, ou encore de connaître le type de design d'alimentation à découpage et son potentiel de fiabilité.

Et bien entendu, ces observations découlent de nos analyses des circuits imprimés et non pas de ce que l'on pourrait éventuellement lire dans d'autres articles sur ces modèles. Par ailleurs, il serait logique qu'un modèle qui introduise la terminaison « Pro » dans son intitulé puisse être utilisé en entreprise, dans des machines qui font du stockage intensif, ou même encore dans des serveurs. Cela sous-entend donc que le module d'alimentation dont il dispose soit irréprochable en terme de robustesse, de stabilité, de protection, et de redondance puisque c'est lui qui gère le courant nécessaire à tous les circuits intégrés du système. Et bien vous risquez d'avoir quelques surprises...

![La magie de la loupe, sans loupe sandisk ultra plus dessus (il aime dominer le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/sandisk/ultraplus-256/sandisk-ultraplus-av_t.jpg)

![Même pas cap' de cliquer sandisk ultra plus derrière (il aime être dominé le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/sandisk/ultraplus-256/sandisk-ultraplus-ar_t.jpg)

![3N C11QU4N7 C357 P1U5 6r4ND sandisk ultra plus pcb conntrolleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/sandisk/ultraplus-256/sandisk-ultraplus-av_pcb_t.jpg)

![Même pas cap' de cliquer sandisk ultra plus pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/sandisk/ultraplus-256/sandisk-ultraplus-ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

Quand on dispose d'une technologie de mémoire NAND de 64Go gravé en 19nm et qu'il n'en faut donc que 4 pour obtenir un SSD de 256Go, on ne s'embête pas à produire un circuit imprimé d'un facteur de forme classique de 95mm quand on peut tout intégrer en 40mm, base Marvell ou non. Et c'est précisément la raison pour laquelle le circuit de ce modèle est aussi compact. Et vu dans son ensemble, il représente d'ailleurs un bijou d'intégration pour une telle capacité de stockage.

Mais cette prouesse ne s’arrête pas uniquement au stockage, il est également très bien conçu d'un point de vue du design électronique. Pour aller de pair avec le contrôleur Marvell 88SS9175, les ingénieurs ont opté pour un régulateur de tension et convertisseur Buck programmable assez complet du même fabricant, qui est là pour gérer et superviser l'alimentation des circuits intégrés non analogiques. Nous n'avons pas pu identifier avec certitude le rôle du circuit intégré AnalogDevice placé entre les 2 puces Marvell. Mais il n'est pas impossible qu'il s'agisse d'un capteur et analyseur de température destiné à renseigner le régulateur intelligent de la température ambiante exacte. Ce qui est sûr, c'est que ce module d'alimentation à découpage est exemplaire pour un système aussi compact, avec une redondance du module principal vers un module auxiliaire identique à tous les étages, y compris au niveau des bobines de filtrage et de la chaîne de condensateurs en céramique.

![Ne pas appuyer ici sandisk extreme pro dessus (il aime dominer le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/sandisk/extreme-pro-480/sandisk-extremepro-av_t.jpg)

![Même pas cap' de cliquer sandisk extreme pro derrière (il aime être dominé le cochon) [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/sandisk/extreme-pro-480/sandisk-extremepro-ar_t.jpg)

![Même pas cap' de cliquer sandisk extreme pro pcb conntrolleur [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/sandisk/extreme-pro-480/sandisk-extremepro-av_pcb_t.jpg)

![Si vous cliquez, vous cliquez. sandisk extreme pro pcb verso [cliquer pour agrandir]](/images/stories/articles/stockage/ssd/sandisk/extreme-pro-480/sandisk-extremepro-ar_pcb_t.jpg)

A oilp et pas (cliquez pour agrandir)

A l'instar de ce que nous a habitué Seagate, Sandisk a conçu là un circuit imprimé simple face avec le soucis de ne poser aucun composant sur la face extérieure pour les protéger d'une éventuelle décharge électrostatique. Cela complique pas mal la répartition et la disposition des composants, et ajoute aussi plus de contraintes dans le tracé des pistes des couches internes du circuit.

On voit tout de suite que l'alimentation a découpage prend une bonne partie de la première moitié de la surface, mais reste cependant bien localisée. Mais du coup, le contrôleur Marvell et sa DRAM ont du être légèrement décentrés, ce qui n'est bien entendu pas un problème en soi. Les 8 mémoires NAND Sandisk en boîtier BGA occupent la totalité de la seconde moitié. Et à propos de l'alimentation, nous restons relativement dubitatif devant le design que l'on a pu retracer ici, non pas qu'il ne soit pas adapté, mais plutôt parce qu'il aurait pu être un brin plus complet pour ce type de modèle. En effet, il n'y a rien à dire du côté des étages de conversion continu-continu assurée par 3 convertisseurs Buck synchrone de chez Texas Instruments et une poignée de régulateurs de tension. Le premier étage dispose d'ailleurs d'un module auxiliaire pour assurer une redondance du système au niveau le plus critique. Cependant, il n'y a aucune trace d'un « chien de garde » qui lui donnerait la protection nécessaire pour décider s'il a besoin d'être réinitialisé, ou bien encore pour être certain que la bonne tension soit présente à tel ou tel endroit critique du circuit.

A ce niveau de conception, on s'attend à ce qu'un SSD dispose de tous les ingrédients connus pour en faire un produit irréprochable, la performance pure ne doit pas être le seul critère qui compte. Et, sans doute pour des raisons de coût, ça n'est visiblement pas toujours le cas...

Article réalisé en collaboration avec Deus Ex Silicium

|

|