Toshiba en avance sur la MRAM |

• 11 Juillet 2011 à 11h38 • 13205 vues

Toshiba en avance sur la MRAM |

• 11 Juillet 2011 à 11h38 • 13205 vues

Peut-être que MRAM cela ne vous dit rien, vous fichiez quoi pendant les cours de physique ? Bref, rappel donc sur cette mémoire magnétorésitive, le saint Graal pour beaucoup qui pourrait bien succéder aux mémoires DRAM et NAND telles que nous les connaissons aujourd'hui avec leurs problèmes respectifs : d'un côté, la nécessité de courant pour la conservation des données, de l'autre l'usure progressive des cellules. La solution parait donc évidente, ne plus avoir recours à l'électricité qui est problématique dans les deux cas, mais à une bonne vieille technologie que nous connaissons tous dans nos disques durs : le magnétisme. Au menu : hautes performances, quasi inusabilité, consommation en baisse, on comprend mieux dès lors pourquoi on parle de convergence des mémoires.

Vient donc la MRAM en développement depuis des lustres chez Motorola, IBM, Infineon, Toshiba, Samsung, NEC, ST Microelectronics, Sony and co, dont il existe déjà des applications commerciales depuis 2006 via la société Freescale. Seul problème ces puces sont limitées en capacité : seulement 4Mb (oui, 0,5Mo !) pour un prix unitaire d'une vingtaine de $. Ce n'est pas gagné pour une barrette de 4Go, et encore moins pour un SSD de 1To.

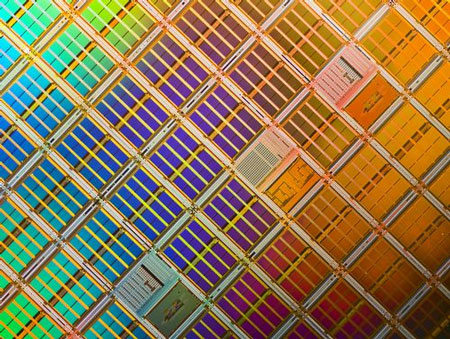

Un wafer de MRAM, parait-il.

C'est là que l'annonce du 6 juillet dernier de la part de Toshiba est intéressante : par principe, l'exploitation des données est basée sur la magnétorésistance à effet tunnel (on distingue la différence de potentiel entre deux couches ferromagnétiques qui emprisonnent des électrons, plus cet écart est fort, plus l'information stockée sera fiable). Pour écrire une donnée, on modifie le sens de rotation des électrons (appelé spin) par un "simple" changement de polarité, à l'aide d'un substrat de jonction. Dans un souci de miniaturisation, les défis actuels reposent sur la mise au point du-dit substrat magnétorésistant permettant de mesurer la différence de potentiel dans un écart réduit, histoire de caser davantage de cellules.

Une belle étape franchie par la firme qui annonçait avoir pu écrire des données avec 6 fois moins d'intensité électrique et avec une différence de potentiel en augmentation de 185%, le tout sur une finesse de 50nm ! Des résultats qui n'étaient pas attendus selon l'ITRS -qui fait autorité dans le monde des semi-conducteurs- avant... 2024. Une perspective qui permettrait la venue sur le marché de puces de 128Mo de STT-MRAM (Spin Torque Transfer Magnetic Random Access Memory... à vos souhaits) à des coûts similaires à ceux de la DDR actuelle d'ici à 2015. Bon, et la PRAM c'est pour quand M. Samsung / IBM ? (source : Tech-On!)

| Un poil avant ?Soldes : Steam continue sur sa lancée, Portal 2, BC 2, Borderlands, etc. | Un peu plus tard ...VIA lance une carte mère mini-ITX avec Nano X2 E intégré |  |