NVIDIA a aussi des chiplets, mais c'est pour l'IA |

• 02 Juillet 2019 à 13h29 • 8936 vues

NVIDIA a aussi des chiplets, mais c'est pour l'IA |

• 02 Juillet 2019 à 13h29 • 8936 vues

Pour le grand public, les chiplets, c'est-à-dire les sous-puces d'une unité hardware assemblées sur un même socket, sont une invention d'AMD. Si il est vrai que le designeur de puces rouge a pour la première fois apporté cette technologie du côté des CPU sur les segment HEDT (enthusiast) avec Threadripper, et chez les pros avec EPYC - et bientôt le grand public avec Zen2 - l'idée était depuis quelque temps déjà en vogue dans les projets de recherches publics expérimentaux.

C'est de l'un de ces projets dont il est question aujourd'hui chez NVIDIA cette fois-ci. Présenté au VLSI Symposium version 2019, la puce nommé RC 18 pour Research Chip 2018 - pas vraiment de quoi exciter les foules comme nom de code ! - pousse ce concept à un tout autre niveau. Certes, il ne s'agit pas d'un CPU mais d'un accélérateur dédié à l'inférence de réseaux de neurones, c'est-à-dire la manipulation consistant à prédire quelque chose à partir d'une structure préalablement entraînée, toutefois sa structure est extrêmement prometteuse.

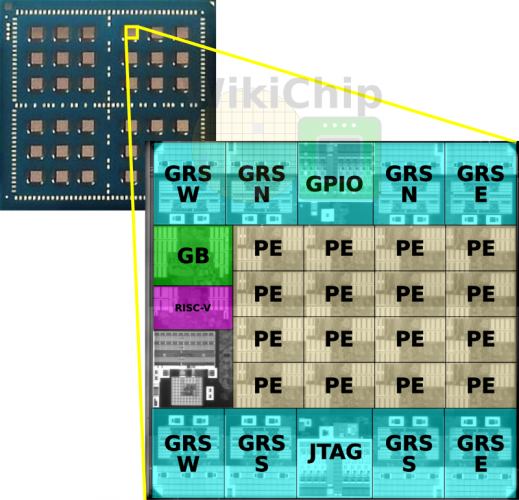

Tout comme le die Zepplin d'AMD, le RC 18 est prévu pour être scalable, comprendre qu'elle peut se lier avec des consoeurs pour un maximum de... 36 dies par socket (ordonnées en 6x6). Des versions à 1x1, 2x2 et 4x4 sont également possible, ce qui permettrait de décliner un gamme commerciale dérivée de ce projet à la fois pour des appareils très basse consommation, des voitures autonomes et des serveurs de calculs, tout ça à partir d'un unique design de 6mm² seulement, le tout sous la houlette du 16nm de chez TSMC.

Est-ce vraiment une surprise de trouver au sein de chaque puce un coeur RISC-V Rocket ? Pas vraiment ! Cet équivalent à un Cortex-A5 (in-order et pipeline à 5 étages) contrôle 16 Processing Elements dédiées aux calculs matriciels, entourés de blocs logiques utilisées lors des communications inter-dies. Le bouzin serait en outre suffisamment optimisé pour dépasser le GHz de fréquence (l'opérateur pourra choisir une valeur entre 161 MHz et 2001 MHz pour une puce seule, l'intervalle se restreignant à 484 MHz - 1797 MHz pour la version à 36 dies), pas mal quand on sait que la principale concurrence de ces bouzins est conduite par... les GPU. Avec ce design, NVIDIA assure une puissance maximale de 1024 multiplications-accumulation par cycle, soit un maximum de 127,8 TOPS pour la mouture la plus grosse à pleine puissance. Dans ce cas, l'ensemble dissipera quelque 110W, plutôt alléchant !

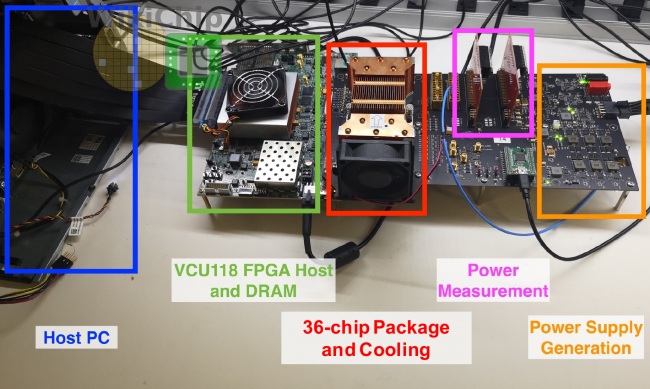

Le premier tape-out du bouzin

Bien qu'il ne s'agisse que d'un prototype, il est difficile d'éviter la comparaison avec les Tensor Cores déjà intégrés dans les puces Turing. Dans le futur, une solution à base de chiplets serait probablement moins coûteuse que les dies monolithiques actuelles, si les contraintes de faible latence induites par les programmes vidéoludiques réussissent à être respectées dans ce type de design. On en reparle dans 5 ans sur les segments pros ? (Source : WikiChip)

| Un poil avant ?Le Deep Learning et les UV extrêmes, un mariage à tenter ? | Un peu plus tard ...Soldes • Sapphire RX 590 Nitro+ à 187,91 € |  |